Part Number: LAUNCHXL-F28379D

Other Parts Discussed in Thread: C2000WARE

Hello there,

I have experimented with sci loopback interrupt examples (using SCIA and SCIB).

I have below questions:

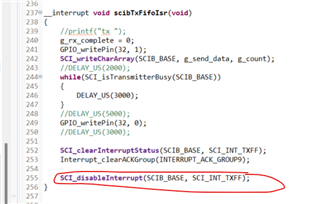

1. How does a TX interrupt got trigger? for instance in sci_ex2_loopback_interrupt example I can understand that Rx interrupt got triggered every time we received something on one of the GPIO pins that we configured to receive the data but how does Tx interrupt got triggered. Are Rx and Tx interrupts taking turns in cyclic fashion?

2. What I am trying to so is, I want to trigger the Tx interrupt lets say when I met certain conditions or when data is ready, I mean I want to control the Tx Interrupt. And also how do I stop the transmission.

Thanks,