Part Number: TMS320F280039C

In your TRM, Table32-1 shows CLB TILE clock is SYSCLK in SYNC Mode. But in Figure 32-3, CLB TILE clock is divied clock of SYSCLK determined by PERCLKDIVSEL.EPWMCLKDIV.

Which statement is correct?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320F280039C

In your TRM, Table32-1 shows CLB TILE clock is SYSCLK in SYNC Mode. But in Figure 32-3, CLB TILE clock is divied clock of SYSCLK determined by PERCLKDIVSEL.EPWMCLKDIV.

Which statement is correct?

Hi Liu Liu,

I believe this diagram was accidentally inherited from F2837xD devices. EPWMCLKDIV is no longer involved in the CLB clock.

I will confirm what the correct clocking connections are for CLB and have this section in the TRM updated.

Thank you,

Luke

Hi Liu Liu,

The CLB clock is derived from PLLRAWCLK (which is also the source for SYSCLK). It is then divided by CLBCLKDIV and TILECLKDIV. There is also the option to synchronize this clock to SYSCLK, which is enabled by default.

I will make sure this diagram is updated in the next TRM release for F28003x.

Thank you,

Luke

More things.

1.Does F28003x have AUXPLL as Figure 32-3? Are the CLBCLKCTL.CLBCLKDIV and CLBCLKCTL.TILECLKDIV registers valid?

I cannot find any description of AUXPLL in the datasheet and TRM of F28003x. Is it PLLRAWCLK?

2.If CLB work in AUXPLL , It will async with other module in SYSCLK. Many CLB's GLB/LCL input from SYSCLK, can CLB work fine?

3.From Figure 3-3, the CLB work in SYSCLK, it is a contradiction with the description in Figure 32-3

Hi Liu Liu,

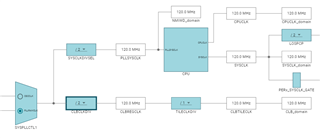

The correct clocking diagram can be found in the clocktree tool:

There is the option to synchronize the CLBTILECLK to SYSCLK after applying the dividers above.

We will update the diagrams in the datasheet and TRM to match this.

Thank you,

Luke

1. I cannot understand this diagram, from TRM.table 3-47, SYSPLLCTL1 used to ctrl sysclk source is from pllrawclk or oscclk.

so the output of SYSPLLCTL1 in the diagram is sysclk? And CLB clk source is sysclk only?

2. But from the TRM.FIGURE32-3 and your reply, I think CLB.tileclk/regclk source is sysclk of AUXPLL(PLLRAWCLK??) which is controlled by CLBCLKCTL.CLKMODECLBx.

1 and 2 conclusions are contradictory.

3. If CLB can work in asynchronous clk with SYSCLK,is there any application on this configuration? Because other module work in SYSCLK(like EPWM/EQEP/ECAP/SPI/FSI/LIN/SCI based on Tbale32-4 and PIE), can CLB output be capture by those module working at SYSCLK?(e.g. If CLB clk is PLLrawCLK at 120MHz and Sysclk is OSCCLK at 10MHz, if CLB generate a interrupt, can this interrupt be received by PIE module working at SYSCLK? )

Hi Liu Liu,

I'm handling several other customer issues at the moment and will need some time to confirm these details, apologies for the delay. Please expect a response before the end of this week.

Thank you,

Luke

Hi Liu Liu,

1. When SYSPLLCTL1.PLLCLKEN and SYSPLLCTL1.PLLEN are both set to 1, PLLRAWCLK will be used as the source clock for both SYSCLK and CLB clock.

2. This diagram is incorrect. The correct diagram is in the clock tree tool:

I have filed a ticket to correct this in the TRM.

3. If CLB clock and SYSCLOCK have the same frequency, I don't believe there is any use case for making CLB clock asynchronous to SYSCLK.

Thank you,

Luke

1. From your interpretation, can I think CLB.CLKCTL.CLKMODECLBx have not any use?

a. CLB tile clk is determined by CLBCLKCTL.TILECLKDIV

b. CLB reg clk is determined by CLBCLKCTL.CLKDIV

2. So how about Table32-1? is it correct?

3. If I run CLB.REG/TILE in 60MHz and SYSCLK is in 120MHz,is there any problem for CLB to receive signal in SYSCLK(e.g ERAD_EVTx)?

4. Is there exist any application for CLB to work in different frequency with SYSCLK?

Hi Liu Liu,

1. CLB should always be synchronized to SYSCLK unless CLB clock is faster than SYSCLK

2. Yes

3. I would recommend using CLB clock at the same frequency as SYSCLK, a lower clock rate for the CLB clock will have an effect on how the CLB inputs are processed.

4. Not to my knowledge. This may reduce power consumption to some extent but I'm not sure whether this is specified in the datasheet.

Thank you,

Luke