Other Parts Discussed in Thread: C2000WARE

Hello Mr. expert,

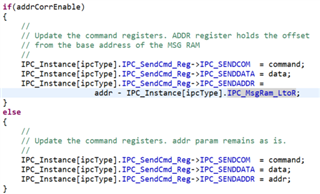

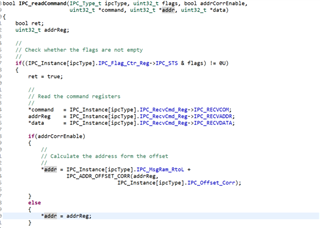

when I examined the ipc c2000ware sample codes IPC_sendCommand(IPC_CPU1_L_CM_R, IPC_FLAG0, IPC_ADDR_CORRECTION_ENABLE, IPC_CMD_READ_MEM, (uint32_t)readData, 10); When I examine the function code, I see such a definition IPC_ADDR_CORRECTION_ENABLE, I searched for its meaning but I could not find anything, can you explain what IPC_ADDR_CORRECTION_ENABLE means?