Part Number: TMS320F28388D

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE, TMDSCNCD28388D

Tool/software:

Hi

I'm trying to get LS7366R iC's register value through SPI however, I have some problems with it and I need some help please cause I couldn't solve these problems for about 3 weeks ...

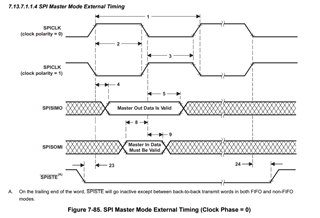

This is the SPI protocol diagram that I want to make between LS7366R(SPI slave) and TMS320F28388D(SPI master).

(This is the diagram from LS7366R datasheet. LS7366R datasheet link : https://lsicsi.com/datasheets/LS7366R.pdf)

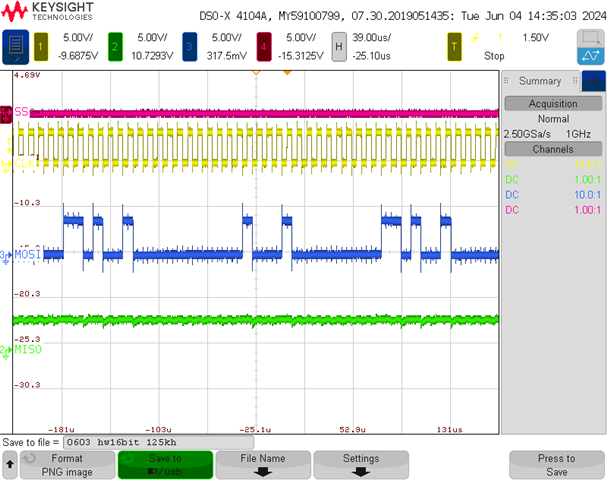

So I set my sysconfig settings, wrote the code, and connected the SPI lines to oscilloscope. These pictures are my sysconfig settings, codes, and oscilloscope signal screenshots.

//#############################################################################

//

// FILE: spi_ex1_loopback.c

//

// TITLE: SPI Digital Loopback

//

//! \addtogroup driver_example_list

//! <h1>SPI Digital Loopback</h1>

//!

//! This program uses the internal loopback test mode of the SPI module. This

//! is a very basic loopback that does not use the FIFOs or interrupts. A

//! stream of data is sent and then compared to the received stream.

//! The pinmux and SPI modules are configure through the sysconfig file.

//!

//! The sent data looks like this: \n

//! 0000 0001 0002 0003 0004 0005 0006 0007 .... FFFE FFFF 0000

//!

//! This pattern is repeated forever.

//!

//! \note This example project has support for migration across our C2000

//! device families. If you are wanting to build this project from launchpad

//! or controlCARD, please specify in the .syscfg file the board you're using.

//! At any time you can select another device to migrate this example.

//!

//! \b External \b Connections \n

//! - None

//!

//! \b Watch \b Variables \n

//! - \b sData - Data to send

//! - \b rData - Received data

//!

//

//#############################################################################

//

//

// $Copyright:

// Copyright (C) 2022 Texas Instruments Incorporated - http://www.ti.com

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//#############################################################################

/*Included Files*/

#include "driverlib.h"

#include "device.h"

#include "board.h"

#include <stdio.h>

/*IR REG*/

//OP CODE

#define CLR_REG 0x00

#define RD_REG 0x40

#define WR_REG 0x80

#define LOAD_REG 0xC0

//SEL REG

#define MDR0 0x00 | (0b001 << 3)

#define MDR1 0x00 | (0b010 << 3)

/*MDR0 SETTING*/

#define MDR0_4QUAD_MODE 0x00 | 0b11

/*MDR1 SETTING*/

#define MDR1_4BYTE_MODE 0x00 | 0b00

#define STE_HIGH GPIO_writePin(SPISTE, 1)

#define STE_LOW GPIO_writePin(SPISTE, 0)

#define STE_STATE GPIO_readPin(SPISTE)

/*private code*/

#define nData 2

uint16_t TxData[nData] = {0,};

uint16_t RxData[nData] = {0,};

/*Main*/

void main(void)

{

/*start settings*/

// Initialize device clock and peripherals

Device_init();

// Disable pin locks and enable internal pullups.

Device_initGPIO();

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

Interrupt_initModule();

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

Interrupt_initVectorTable();

// Board initialization

Board_init();

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

EINT;

ERTM;

/*USER CODE*/

STE_HIGH;

while(1)

{

STE_LOW;

TxData[0] = (WR_REG | MDR0);

TxData[1] = (MDR0_4QUAD_MODE);

SPI_writeDataBlockingNonFIFO(mySPI0_BASE, (TxData[0] << 8U));

SPI_writeDataBlockingNonFIFO(mySPI0_BASE, (TxData[1] << 8U));

// DEVICE_DELAY_US(200);

STE_HIGH;

DEVICE_DELAY_US(20);

// DEVICE_DELAY_US(1000);

//

// STE_LOW;

// SPI_writeDataBlockingNonFIFO(mySPI0_BASE, (RD_REG | MDR0) << 8U);

// RxData[0] = SPI_readDataBlockingNonFIFO(mySPI0_BASE);

// DEVICE_DELAY_US(20);

// STE_HIGH;

//

// DEVICE_DELAY_US(1000);

}

}

//

// End File

//

CLK should only work when STE == LOW, CLK also works when STE == HIGH.

If you look at the logic of the main code, there is absolutely no reason for CLK to work because it raises STE to HIGH after the data transmit, but I don't know why it's like this.

Looking at the oscilloscope waveform, SPI_writeDataBlockingNonFIFO and STE seem to operate independently.

Is this because of the operation of STE with GPIO? I don't know why...

In order to solve the problem of not working when the data transfer function is in the STE==LOW state, DEVICE_DELAY_US (200) was arbitrarily given between SPI_writeDataBlockingNonFIFO and STE_HIGH, and the following waveform was taken.

At this time, when looking at the STE(=SS) waveform, the LOW state is maintained exactly about 200us.

So, I wrote it in order on the code, but do GPIO and SPI move independently? How should I look at this phenomenon?

And if this is a problem caused by controlling with GPIO, how should I set it up in the SPI of sysconfig to send two 8bit data in a row?