Other Parts Discussed in Thread: C2000WARE

Tool/software:

Our project used to run fine. The project contains a few modules which are all logically correct, which is verified in some way. But one module, let me call it "Module1", seems to have caused some memory issue.

- If commenting out "Module1", the whole project runs fine.

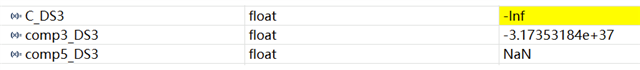

- If including "Module1", when running the project, some variables become strange, such as "-Inf" "NaN". "-Inf" means "minus infinite" and "NaN" means "not a number"? Below is the screen capture of the "Expression tab":

These variables are defined in "cla_shared" because they are used by both CPU and CLA

I believe it is a memory issue because "Module1" is logically correct. I guess there are 2 possibilities:

- stack overflow happened, or

- dynamic memory allocation (heap) issue

I tried to increase stack and heap size but failed to resolve the problem. Below is the .cmd file; could you advise how to fix it?

==========

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002 // Update the codestart location as needed

BOOT_RSVD : origin = 0x000002, length = 0x000126 /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x000128, length = 0x0002D8

RAMM1 : origin = 0x000400, length = 0x000400

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

/* Quentin 20240307: Combining all the LS RAMs */

//RAMLS012 : origin = 0x008000, length = 0x001800

//RAMLS12 : origin = 0x008800, length = 0x001000

RAMLS3 : origin = 0x009800, length = 0x000800

// RAMLS4 : origin = 0x00A000, length = 0x000800

// RAMLS5 : origin = 0x00A800, length = 0x000800

// RAMLS6 : origin = 0x00B000, length = 0x000800

// RAMLS7 : origin = 0x00B800, length = 0x000800

/* Quentin 20240110: Combining all the LS RAMs */

RAMLS4567 : origin = 0x00A000, length = 0x002000

RAMLS8 : origin = 0x014000, length = 0x002000 // When configured as CLA program use the address 0x4000

RAMLS9 : origin = 0x016000, length = 0x002000 // When configured as CLA program use the address 0x6000

// RAMLS8_CLA : origin = 0x004000, length = 0x002000 // Use only if configured as CLA program memory

// RAMLS9_CLA : origin = 0x006000, length = 0x002000 // Use only if configured as CLA program memory

//RAMGS0 : origin = 0x00C000, length = 0x002000

//RAMGS1 : origin = 0x00E000, length = 0x002000

RAMGS01 : origin = 0x00C000, length = 0x004000

RAMGS2 : origin = 0x010000, length = 0x002000

RAMGS3 : origin = 0x012000, length = 0x002000

/* Flash Banks (128 sectors each) */

FLASH_BANK0 : origin = 0x080002, length = 0x1FFFE

FLASH_BANK1 : origin = 0x0A0000, length = 0x20000

FLASH_BANK2 : origin = 0x0C0000, length = 0x20000

FLASH_BANK3 : origin = 0x0E0000, length = 0x20000

FLASH_BANK4 : origin = 0x100000, length = 0x20000

CLATOCPURAM : origin = 0x001480, length = 0x000080

CPUTOCLARAM : origin = 0x001500, length = 0x000080

CLATODMARAM : origin = 0x001680, length = 0x000080

DMATOCLARAM : origin = 0x001700, length = 0x000080

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN

.text : >> FLASH_BANK0 | FLASH_BANK1, ALIGN(8)

.cinit : > FLASH_BANK0, ALIGN(8)

.switch : > FLASH_BANK0, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

//.stack : > RAMM1

// Quentin 20240307: change .stack from RAMM1 to RAMLS0 for more space

//.stack : > RAMLS0

// Quentin 20240424: change .stack from RAMLS0 to RAMGS0: 1. for more stack space 2. for RAMLS0 used for CLA

//.stack : > RAMGS0

.stack : > RAMGS01

#if defined(__TI_EABI__)

//.bss : > RAMLS5

.bss : > RAMLS4567

//.bss:output : > RAMLS3

// Quentin 20240323: replace line above with line below, to leave RAMLS3 for other usage

//.bss:output : > RAMLS12

// Quentin 20240323: since I am not sure about correct usage of RAMLS8 as CLA memory, replace line above with line below to change from using RAMLS12 to RAMLS8

//.bss:output : > RAMLS8

// Quentin 20240525 : I am afraid putting .sysmem & .data together at RAMLS8 might cause problem, so replace RAMLS8 with RAMGS2

.bss:output : > RAMGS2

.init_array : > FLASH_BANK0, ALIGN(8)

.const : > FLASH_BANK0, ALIGN(8)

//.data : > RAMLS5 | RAMLS6

//.data : > RAMGS0

// Quentin 20240307: to prevent stack overflow to GSRAM, replace line(RAMGS0) above with line below(RAMLS12):

//.data : > RAMLS12

// Quentin 20240323: since I am not sure about correct usage of RAMLS8 as CLA memory, replace line above with line below to change from using RAMLS12 to RAMLS8

//.data : > RAMLS8

.data : > RAMLS9

//.sysmem : > RAMLS4

//.sysmem : > RAMGS0

// Quentin 20240307: to prevent stack overflow to GSRAM, replace line(RAMGS0) above with line below(RAMLS12):

//.sysmem : > RAMLS12

// Quentin 20240323: since I am not sure about correct usage of RAMLS8 as CLA memory, replace line above with line below to change from using RAMLS12 to RAMLS8

//.sysmem : > RAMLS8

// Quentin 20240525 : I am afraid putting .sysmem & .data together at RAMLS8 might cause problem, so replace RAMLS8 with RAMGS3

.sysmem : > RAMGS3

#else

.pinit : > FLASH_BANK0, ALIGN(8)

//.ebss : >> RAMLS5 | RAMLS6

.ebss : >> RAMLS4567

.econst : > FLASH_BANK0, ALIGN(8)

//.esysmem : > RAMLS5

.esysmem : > RAMLS4567

#endif

//ramgs0 : > RAMGS0

//ramgs1 : > RAMGS1

ramgs2 : > RAMGS2

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH_BANK0,

//RUN = RAMLS0,

RUN = RAMLS4567,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH_BANK0,

//RUN = RAMLS0,

RUN = RAMLS4567,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

/* CLA specific sections */

#if defined(__TI_EABI__)

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK0,

RUN = RAMLS0,

LOAD_START(Cla1ProgLoadStart),

RUN_START(Cla1ProgRunStart),

LOAD_SIZE(Cla1ProgLoadSize),

ALIGN(4)

#else

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK0,

RUN = RAMLS0,

LOAD_START(_Cla1ProgLoadStart),

RUN_START(_Cla1ProgRunStart),

LOAD_SIZE(_Cla1ProgLoadSize),

ALIGN(4)

#endif

// below is from F28P55 cla_ex4_pwm_control example project (20240419)

Cla1ToCpuMsgRAM : > CLATOCPURAM

CpuToCla1MsgRAM : > CPUTOCLARAM

.scratchpad : > RAMLS1

.bss_cla : > RAMLS1

Cla1DataRam : > RAMLS2

cla_shared : > RAMLS1

CLADataLS1 : > RAMLS1

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH_BANK0,

RUN = RAMLS1,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

ALIGN(4)

#else

.const_cla : LOAD = FLASH_BANK0,

RUN = RAMLS1,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

ALIGN(4)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

CLA shared memory