Tool/software:

Team,

-I understand from the below thread that CPU2 is always independent from CPU1 (whether or not Lockstep on CPU2 is available on the specific variant).

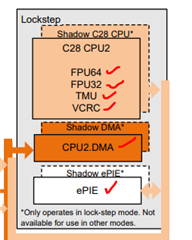

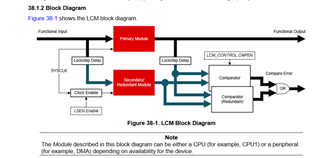

The lockstep feature is specifically between CPU2 and the shadow CPU of CPU2. Correct?

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1358988/tms320f28p659dk-q1-lockstep-function-is-optional/5185575#5185575

Now my question specifically about CPU2:

-For variant with dual CPUs (ie CPU1 and CPU2) but without Lockstep (like DK7, DK6, DH6) are FPU64/FPU32/TMU/VCRC available in CPU2?

-For variant with dual CPUs (ie CPU1 and CPU2) with Lockstep (like DK9, DK8) are FPU64/FPU32/TMU/VCRC physically present in both CPU2 and in the shadow CPU of CPU2?

Looking at F28P65x TRM https://www.ti.com/lit/pdf/spruiz1:

It could make sense in the F28P65x datasheet to describe precisely what is included in what we call the "primary module" in the F28P65x TRM https://www.ti.com/lit/pdf/spruiz1

Thanks in advance,

Anthony