Tool/software:

Hi Champ,

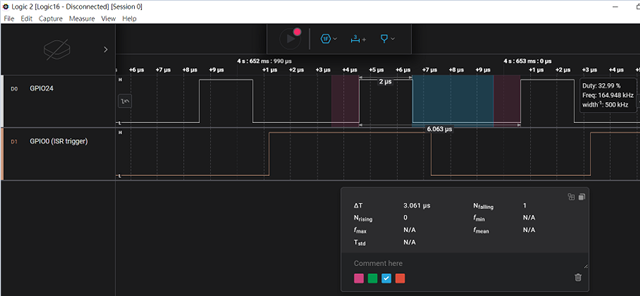

I am asking for my customer. They are using CLB as an auxiliary PWM generator.

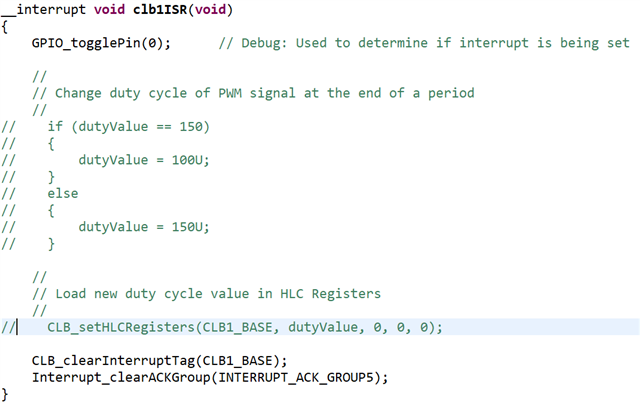

With the similar post from below, user wants to modify the counter Match1/2_ref value in real time or in ISR.

Would the CLB expert kindly help on this ? Please explicitly show how to configure with driverAPI.

Thanks for the support.

Regards,

Johnny

(SPRUIR8B)

(SPRUIR8B) (example default configuration)

(example default configuration)