Other Parts Discussed in Thread: C2000WARE, SYSCONFIG

Tool/software:

HI,

I was able to get the biss interface code setup and start code from TI into the CLA and everything is working so far.

For performance reasons we would like to have the setup/start biss interface to run in the CLA on CPU2 and trigger the SPI RX ISR in CPU1.

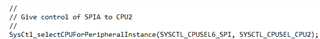

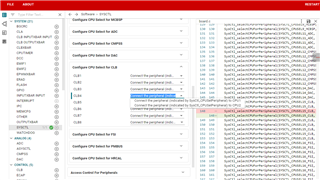

I would suggest not focusing on BISS, really what we need to do is have CPU2/CLA start a SPI request and have CPU1 service the SPI RX ISR.

One issue I have bumped into is that the start operation requires flushing the SPI interface which would need to be own by CPU2 right? secondly if CPU1 needs to process the ISR and uses the SPI how does it get it back.

Is this possible any advice on how to get it functioning would be great.

Dorion