Tool/software:

I am currently facing an issue that I have been unable to resolve. I am using EMIF1 CS4 to perform FPGA read and

write operations and to verify the program. I need assistance with this.

while(1)

{

fmemPtr = (uint16 *)FPGA_Start_Address;

ESC_Value = *fmemPtr; // EMIF1 CS4 Read

DELAY_US(10);

FPGA_PWM_ON(); // EMIF1 CS4 Write

}

#define FPGA_Start_Address 0x00380000

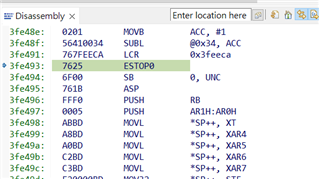

Using the FPGA tool, Signal Tap Logic Analyzer, as shown in the figure below.

"The DSP Data Bus has an output of 0x0005, but the value cannot be found at address 0x00380000 in the DSP Memory Browser.

What other areas should I check?"