Part Number: TMS320F28P550SJ

Tool/software:

Hi champs,

I am asking this for our customer.

In TRM,

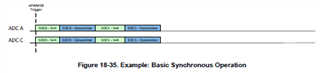

14.12.1 Ensuring Synchronous Operation

We need to sync between ADC modules.

The user also needs to use ADC oversampling by PPB, do they need to consider them both?

If yes, how do they handle both ADC module sync and HW oversampling?

Would you please show us an example explicitly?

For example,

In ADC A and ADC B, they use SOC0-5.

In ADC C, they user SOC0 for oversampling.

How should they do?