Tool/software:

Dear Experts,

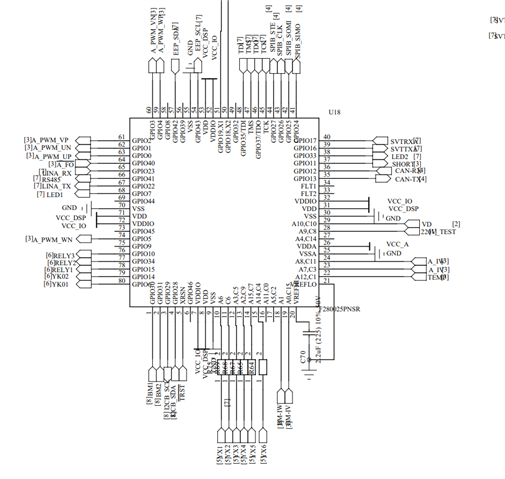

My customer encountered a situation where the chip did not work after powering on the 280025PNSR during production. The program was able to download normally, but it did not work. The measured voltage of the chip's 3.3V power supply pin was normal, and the 1.2V power supply pin was also normal. The waveform of the reset pin is shown in Figure 2. The reset delay is due to the addition of the SP809-2.9 chip, which delayed the reset by 230ms. Please help provide some suggestions for troubleshooting the abnormality. Currently, the customer has not changed the hardware and software, and some are working normally while others are abnormal

yellow is VCC_IO ; Green is XRSN; Blue is VCC_DSP