Other Parts Discussed in Thread: TINA-TI, SYSCONFIG, TMS320F28P659DK-Q1,

Tool/software:

Hello,

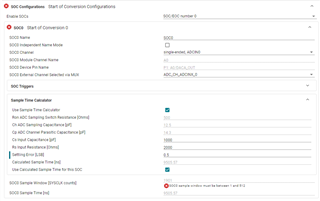

I'm trying to read the same analog signal on two different ADC inputs.

The pin I'm using is GPIO205

I'm reading the signal on C4 and on B28.

The reading is triggered by PWM1 @300KHz for both ADC, 12 bit resolution.

Both C4 and B28 return the same value.

The problem is that when I read both C4 and B28 the value is different from the case in which I read only C4.

The difference is about 20/4096 digits.

If I trigger the reading of B28 on a different pwm (PWM3, still @300KHz):

both C4 and 28 return the same value and in this case it's the same of the case in which I read only C4.

So for my application I've solved using a different trigger, but I would like to understand the reason.

Please consider also that I've also other ADC that are triggered by PWM1.

Is there a limit of ADC that I can trigger with the same PWM? Can be the issue related to the frequency?

..other limitations?

Thankyou