Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Champs,

I am asking this for our customer.

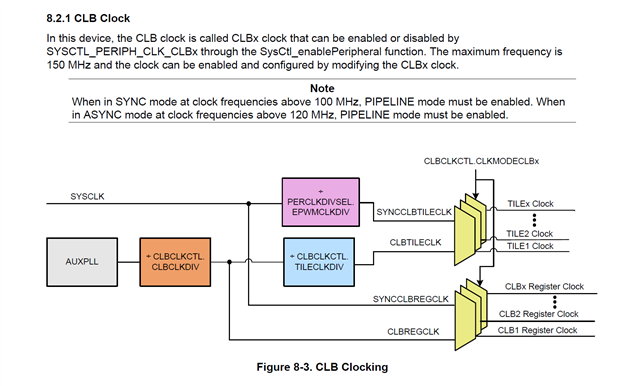

When the user uses SYSCLK = EPWMCLK = 200 MHz, does that mean CLB clock can be 100 MHz at maximum because CLB clock cannot exceed 150 MHz in 8.2.1 CLB Clock of TRM ?

(Note that SYSCLK = EPWMCLK = 200 MHz is a hard requirement here.)

Q1:

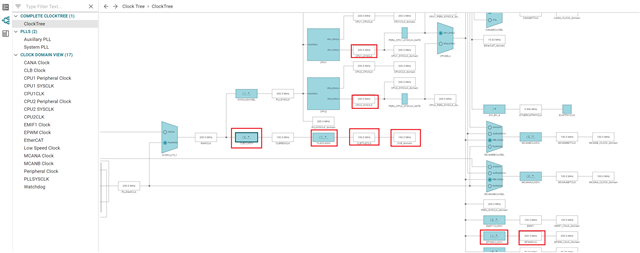

We uses Sysconfig Clocktree below.

Would you please confirm the configuration below is correct?

Q2:

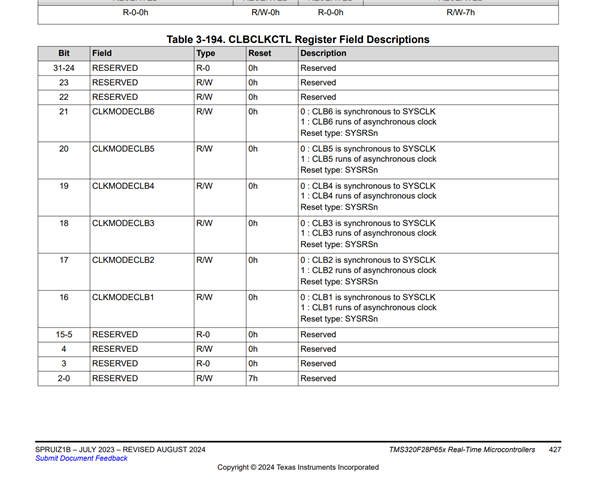

In TRM Table 3-194 below for CLBCLKCTL, the bits are reserved. The user does not see CLBCLKDIV, TILECLKDIV.

Is there anything wrong?

By using Sysconfig clocktree above, can CLB clock be set correctly?