Part Number: TMS320F280049C

Other Parts Discussed in Thread: C2000WARE

Tool/software:

Hi

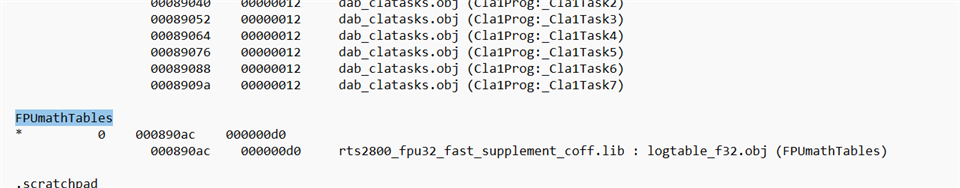

When I stuy TI DSP280049C Live DFU example, I have a questions about the Example "C:\ti\c2000\C2000Ware_DigitalPower_SDK_5_02_01_00\c2000ware\driverlib\f28004x\examples\flash\flashapi_ex2_sci_kernel"

Question as below:

(1) I noticed the the kernel is put in flash memory in CMD file,but I saw the document says the Kernel should run in RAM and then it can receive application data and erase、programme flash, but here why put kernel in flash? How does it work?