Tool/software:

Hi Team,

I have two questions about connection with ET1100, could you please help to clarify? Thanks.

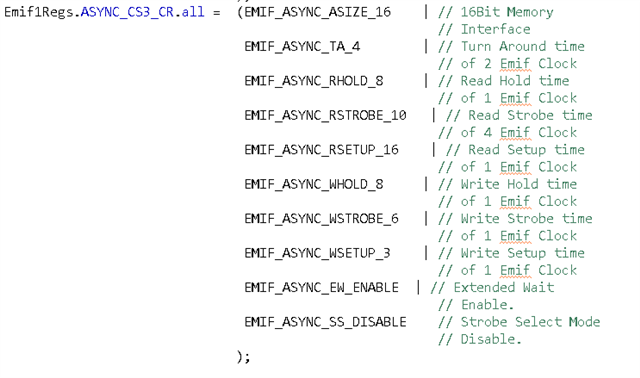

1. ET1100 is connected to TI's 28377 via the EMIF port. Can the ET1100 be accessed in 100ns cycles if the busy signal is enabled? Or do I need to meet write cycles greater than 280 ns for the timing to be safe?

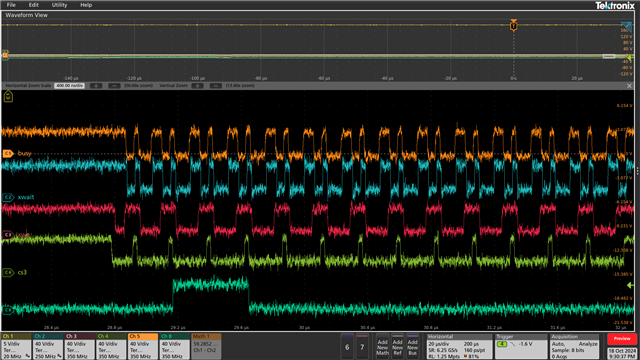

2. The busy signal goes to the Xwait signal of the DSP, but it does not pass through the FPGA, with about 10 ns of delay. Is there any adjustment needed on the timing sequence design?