Part Number: TMS320F28388D

Tool/software:

Hello,

I am working on setting up an SPI peripheral with the SPI clock (SPI-CLK) sourced from a clock generated by the CLB.

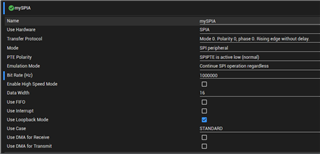

To test this configuration, I attempted to use the SPI loopback mode. The SPI setup is shown in the attached configuration image.

Here are the details of my setup:

- I have generated the clock (1MHz) via the CLB and connected this signal to the SPI CLK pin through GPIOs.

- The SPI PTE pin is connected to ground, also via GPIOs.

- I am monitoring all of these signals using an oscilloscope.

When the SPI is in Controller/Master mode, with the CLB clock disconnected from the SPI CLK pin, the loopback works correctly.

However, when I switch the SPI to Peripheral mode and connect the CLB clock to the SPI CLK pin, the SPI POCI pin (MISO) remains high. I have verified the contents of the SPI TXBUF and SPIDAT registers. While SPI TXBUF shows the expected value, SPIDAT consistently reads 0xFFFF.

Any insights into what might be causing this issue would be greatly appreciated.

Is it possible to use loopback mode with SPI in Peripheral mode?

Thank you!

Regards,

Wilko