Part Number: TMS320F280045

Tool/software:

Hi experts,

My customer is develop HRPWM function on 280025. The meet the follow issues:

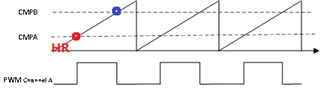

1. For single PWM module, if they enable enable CMPAHR, CMPB and TBPRDHR at the same time. The HR duty cannot work normal.

As the picture shows. Count mode is up mode. The CMPA is HR. The CMPB is normal CMP. TBCLK: 100MHz, PWM period: 400ns

They meet the issue that they set the duty is 204ns but the real duty is 200ns. It seems that CMAHR is not in effect. However, if they remove CMPB, the CMAHR will in effect.

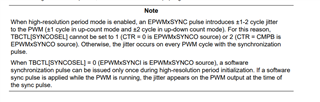

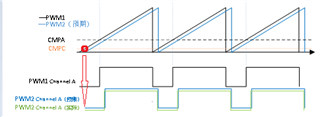

2. For dual PWM module, If they use PWM1 to synchronize PWM2, the period value of PWM2 will fluctuate.

As the picture shows, Count mode is up mode. The CMPA for PWM1 and PWM2 is HR. TBCLK: 100MHz, PWM period: 2857ns. CMPC in PWM1 will sync PWM2.

They meet the issue that, the real period value of PWM2 will fluctuate between 2864ns and 2848ns, the period of PWM1 is OK. However, if they disable the sync and make PWM2 run independently, the real period of PWM2 is OK

The register values are as follow

521177 40 R EPwm1Regs_TBCTL 0x0000000F 0x0030 R EPwm1Regs_TBCTL2 0x0000000F 0x5000 R EPwm1Regs_TBCTR 0x0000000F 0x00ED R EPwm1Regs_TBSTS 0x0000000F 0x0001 R EPwm1Regs_CMPCTL 0x0000000F 0x0000 R EPwm1Regs_CMPCTL2 0x0000000F 0x0000 R EPwm1Regs_DBCTL 0x0000000F 0x002B R EPwm1Regs_DBCTL2 0x0000000F 0x0000 R EPwm1Regs_AQCTL 0x0000000F 0x0000 R EPwm1Regs_AQTSRCSEL 0x0000000F 0x0000 R EPwm1Regs_PCCTL 0x0000000F 0x0000 R EPwm1Regs_VCAPCTL 0x0000000F 0x0000 R EPwm1Regs_VCNTCFG 0x0000000F 0x0000 R EPwm1Regs_HRCNFG 0x0000000F 0x0343 R EPwm1Regs_HRPWR 0x0000000F 0x0028 R EPwm1Regs_HRMSTEP 0x0000000F 0x0049 R EPwm1Regs_HRCNFG2 0x0000000F 0x0000 R EPwm1Regs_HRPCTL 0x0000000F 0x0001 R EPwm1Regs_TRREM 0x0000000F 0x007D R EPwm1Regs_GLDCTL 0x0000000F 0x0000 R EPwm1Regs_GLDCFG 0x0000000F 0x0000 R EPwm1Regs_EPWMXLINK 0x0000000B 0x00000000 R EPwm1Regs_AQCTLA 0x0000000F 0x0210 R EPwm1Regs_AQCTLA2 0x0000000F 0x0000 R EPwm1Regs_AQCTLB 0x0000000F 0x0210 R EPwm1Regs_AQCTLB2 0x0000000F 0x0000 R EPwm1Regs_AQSFRC 0x0000000F 0x0000 R EPwm1Regs_AQCSFRC 0x0000000F 0x0000 R EPwm1Regs_DBREDHR 0x0000000F 0x0000 R EPwm1Regs_DBRED 0x0000000F 0x0000 R EPwm1Regs_DBFEDHR 0x0000000F 0x0000 R EPwm1Regs_DBFED 0x0000000F 0x0000 R EPwm1Regs_TBPHS 0x0000000B 0x00000000 R EPwm1Regs_TBPRDHR 0x0000000F 0xB700 R EPwm1Regs_TBPRD 0x0000000F 0x011C R EPwm1Regs_CMPA 0x0000000B 0x00A90000 R EPwm1Regs_CMPB 0x0000000B 0x001B0000 R EPwm1Regs_CMPC 0x0000000F 0x0001 R EPwm1Regs_CMPD 0x0000000F 0x0000 R EPwm1Regs_GLDCTL2 0x0000000F 0x0000 R EPwm1Regs_SWVDELVAL 0x0000000F 0x0000 R EPwm1Regs_TZSEL 0x0000000F 0x8000 R EPwm1Regs_TZDCSEL 0x0000000F 0x0080 R EPwm1Regs_TZCTL 0x0000000F 0x000A R EPwm1Regs_TZCTL2 0x0000000F 0x0000 R EPwm1Regs_TZCTLDCA 0x0000000F 0x0000 R EPwm1Regs_TZCTLDCB 0x0000000F 0x0000 R EPwm1Regs_TZEINT 0x0000000F 0x0000 R EPwm1Regs_TZFLG 0x0000000F 0x0000 R EPwm1Regs_TZCBCFLG 0x0000000F 0x0000 R EPwm1Regs_TZOSTFLG 0x0000000F 0x0000 R EPwm1Regs_TZCLR 0x0000000F 0x0000 R EPwm1Regs_TZCBCCLR 0x0000000F 0x0000 R EPwm1Regs_TZOSTCLR 0x0000000F 0x0000 R EPwm1Regs_TZFRC 0x0000000F 0x0000 R EPwm1Regs_ETSEL 0x0000000F 0x0000 R EPwm1Regs_ETPS 0x0000000F 0x0000 R EPwm1Regs_ETFLG 0x0000000F 0x0000 R EPwm1Regs_ETCLR 0x0000000F 0x0000 R EPwm1Regs_ETFRC 0x0000000F 0x0000 R EPwm1Regs_ETINTPS 0x0000000F 0x0000 R EPwm1Regs_ETSOCPS 0x0000000F 0x0000 R EPwm1Regs_ETCNTINITCTL 0x0000000F 0x0000 R EPwm1Regs_ETCNTINIT 0x0000000F 0x0000 R EPwm1Regs_DCTRIPSEL 0x0000000F 0x0F00 R EPwm1Regs_DCACTL 0x0000000F 0x0000 R EPwm1Regs_DCBCTL 0x0000000F 0x0002 R EPwm1Regs_DCFCTL 0x0000000F 0x0000 R EPwm1Regs_DCCAPCTL 0x0000000F 0x0000 R EPwm1Regs_DCFOFFSET 0x0000000F 0x0000 R EPwm1Regs_DCFOFFSETCNT 0x0000000F 0x0000 R EPwm1Regs_DCFWINDOW 0x0000000F 0x0000 R EPwm1Regs_DCFWINDOWCNT 0x0000000F 0x0000 R EPwm1Regs_DCCAP 0x0000000F 0x0000 R EPwm1Regs_DCAHTRIPSEL 0x0000000F 0x0000 R EPwm1Regs_DCALTRIPSEL 0x0000000F 0x0000 R EPwm1Regs_DCBHTRIPSEL 0x0000000F 0x0640 R EPwm1Regs_DCBLTRIPSEL 0x0000000F 0x0000 R EPwm1Regs_EPWMLOCK 0x0000000B 0x00000000 R EPwm1Regs_HWVDELVAL 0x0000000F 0x0000 R EPwm1Regs_VCNTVAL 0x0000000F 0x0000 R EPwm2Regs_TBCTL 0x0000000F 0x2004 R EPwm2Regs_TBCTL2 0x0000000F 0x4000 R EPwm2Regs_TBCTR 0x0000000F 0x00BC R EPwm2Regs_TBSTS 0x0000000F 0x0003 R EPwm2Regs_CMPCTL 0x0000000F 0x0000 R EPwm2Regs_CMPCTL2 0x0000000F 0x0000 R EPwm2Regs_DBCTL 0x0000000F 0x002B R EPwm2Regs_DBCTL2 0x0000000F 0x0000 R EPwm2Regs_AQCTL 0x0000000F 0x0000 R EPwm2Regs_AQTSRCSEL 0x0000000F 0x0000 R EPwm2Regs_PCCTL 0x0000000F 0x0000 R EPwm2Regs_VCAPCTL 0x0000000F 0x0000 R EPwm2Regs_VCNTCFG 0x0000000F 0x0000 R EPwm2Regs_HRCNFG 0x0000000F 0x0343 R EPwm2Regs_HRPWR 0x0000000F 0x0000 R EPwm2Regs_HRMSTEP 0x0000000F 0x0000 R EPwm2Regs_HRCNFG2 0x0000000F 0x0000 R EPwm2Regs_HRPCTL 0x0000000F 0x0005 R EPwm2Regs_TRREM 0x0000000F 0x0000 R EPwm2Regs_GLDCTL 0x0000000F 0x0000 R EPwm2Regs_GLDCFG 0x0000000F 0x0000 R EPwm2Regs_EPWMXLINK 0x0000000B 0x00001110 R EPwm2Regs_AQCTLA 0x0000000F 0x0210 R EPwm2Regs_AQCTLA2 0x0000000F 0x0000 R EPwm2Regs_AQCTLB 0x0000000F 0x0210 R EPwm2Regs_AQCTLB2 0x0000000F 0x0000 R EPwm2Regs_AQSFRC 0x0000000F 0x0000 R EPwm2Regs_AQCSFRC 0x0000000F 0x0000 R EPwm2Regs_DBREDHR 0x0000000F 0x0000 R EPwm2Regs_DBRED 0x0000000F 0x0000 R EPwm2Regs_DBFEDHR 0x0000000F 0x0000 R EPwm2Regs_DBFED 0x0000000F 0x0000 R EPwm2Regs_TBPHS 0x0000000B 0x00000000 R EPwm2Regs_TBPRDHR 0x0000000F 0xB700 R EPwm2Regs_TBPRD 0x0000000F 0x011C R EPwm2Regs_CMPA 0x0000000B 0x01050000 R EPwm2Regs_CMPB 0x0000000B 0x00770000 R EPwm2Regs_CMPC 0x0000000F 0x0000 R EPwm2Regs_CMPD 0x0000000F 0x0000 R EPwm2Regs_GLDCTL2 0x0000000F 0x0000 R EPwm2Regs_SWVDELVAL 0x0000000F 0x0000 R EPwm2Regs_TZSEL 0x0000000F 0x8000 R EPwm2Regs_TZDCSEL 0x0000000F 0x0080 R EPwm2Regs_TZCTL 0x0000000F 0x000A R EPwm2Regs_TZCTL2 0x0000000F 0x0000 R EPwm2Regs_TZCTLDCA 0x0000000F 0x0000 R EPwm2Regs_TZCTLDCB 0x0000000F 0x0000 R EPwm2Regs_TZEINT 0x0000000F 0x0000 R EPwm2Regs_TZFLG 0x0000000F 0x0000 R EPwm2Regs_TZCBCFLG 0x0000000F 0x0000 R EPwm2Regs_TZOSTFLG 0x0000000F 0x0000 R EPwm2Regs_TZCLR 0x0000000F 0x0000 R EPwm2Regs_TZCBCCLR 0x0000000F 0x0000 R EPwm2Regs_TZOSTCLR 0x0000000F 0x0000 R EPwm2Regs_TZFRC 0x0000000F 0x0000 R EPwm2Regs_ETSEL 0x0000000F 0x0000 R EPwm2Regs_ETPS 0x0000000F 0x0000 R EPwm2Regs_ETFLG 0x0000000F 0x0000 R EPwm2Regs_ETCLR 0x0000000F 0x0000 R EPwm2Regs_ETFRC 0x0000000F 0x0000 R EPwm2Regs_ETINTPS 0x0000000F 0x0000 R EPwm2Regs_ETSOCPS 0x0000000F 0x0000 R EPwm2Regs_ETCNTINITCTL 0x0000000F 0x0000 R EPwm2Regs_ETCNTINIT 0x0000000F 0x0000 R EPwm2Regs_DCTRIPSEL 0x0000000F 0x0F00 R EPwm2Regs_DCACTL 0x0000000F 0x0000 R EPwm2Regs_DCBCTL 0x0000000F 0x0002 R EPwm2Regs_DCFCTL 0x0000000F 0x0000 R EPwm2Regs_DCCAPCTL 0x0000000F 0x0000 R EPwm2Regs_DCFOFFSET 0x0000000F 0x0000 R EPwm2Regs_DCFOFFSETCNT 0x0000000F 0x0000 R EPwm2Regs_DCFWINDOW 0x0000000F 0x0000 R EPwm2Regs_DCFWINDOWCNT 0x0000000F 0x0000 R EPwm2Regs_DCCAP 0x0000000F 0x0000 R EPwm2Regs_DCAHTRIPSEL 0x0000000F 0x0000 R EPwm2Regs_DCALTRIPSEL 0x0000000F 0x0000 R EPwm2Regs_DCBHTRIPSEL 0x0000000F 0x0640 R EPwm2Regs_DCBLTRIPSEL 0x0000000F 0x0000 R EPwm2Regs_EPWMLOCK 0x0000000B 0x00000000 R EPwm2Regs_HWVDELVAL 0x0000000F 0x0000 R EPwm2Regs_VCNTVAL 0x0000000F 0x0000