Part Number: TIDM-DC-DC-BUCK

Other Parts Discussed in Thread: BOOSTXL-BUCKCONV, SYSCONFIG

Tool/software:

Hi.

I am learning how to program the C2000 to control the eval board BOOSTXL-BUCKCONV. I was studying the code of the buck-F28004x and I found a part that it is difficult to understand. So in the function

BUCK_HAL_setupSyncBuckPwm();

there is an function that it is called

EPWM_setCounterCompareShadowLoadMode(BUCK_DRV_EPWM_BASE,

EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_PERIOD);

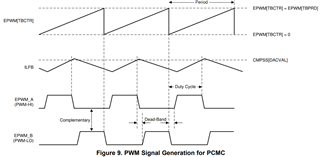

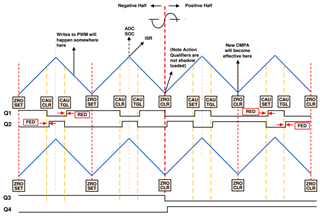

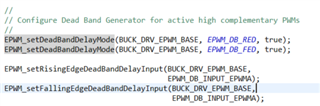

I understand what it does, but my question is: how do I determine whether to use LOADAMODE = 0, 1, or 2? My understanding is that the COMPA register will be updated either at the beginning of the duty cycle or after TBCTR = TBPRD, with the counter being updated in the next cycle.

For voltage mode control, the code uses 0x01. Why not 0x00, for example? If I choose peak current mode control, should I use 0x00 because the counter needs to be updated immediately?