Tool/software:

Hi,

I have 4 PWMs in use.

PWM8 is running on CPU1, PWM1,3,5 are running on CPU2. PWM8 ISR on CPU2 is tied to CPU2/CLA Task 1 ISR.

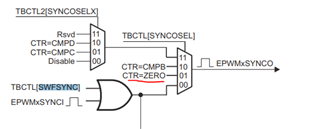

PWM8 is the master synchronization (in the future I need PWM8 to sync to EtherCAT Sync0 pulse).

PWM1 is tied to the output signal from PWM8 and PWM3&5 are tied to PWM 1 output signal

PWM1 is running at 50 and PWM8 is running 4 times slower at 200.

PWM8 is counting UP, PWM1,3,5 are counting up/down.

When PWM8 hits 0, I want PWM1 to sync to 0, which in turn causes 3&5 to sync to 0 and PWM1 0 count cause an interrupt to the processor.

I have enabled all the PWM's here and I have shadow mode enabled.

I can see when PWM8 hits zero that PWM1 goes to zero and causes the ISR, so I know that they are in sync.

Where I am running into an issue is the following:

- If we are configuring the system I have a flag in PWM1 ISR handler to pretty much just ack the ISR signals and leave.

- All the PWM's are running we just don't do anything when we get the PWM1 ISR until configuration is done.

- When configuration is done and when the CLA Task 1 Finished ISR is called (for the first time) it will enable the flag (in item 1)

- On the next PWM1 ISR we will process data. I see that when this is enabled that we get an ISR about 1 USEC later and we process the ISR normally. I am looking at the counters.

What happens next is odd. We will get another PWM1 ISR where the PWM Counts are 18 useconds later instead of being close to zero.

We should only be getting an ISR when the counters are zero in PWM1,

There doesn't appear to be anything pending.

Is there any reason why this would happen?