Part Number: TMS320F28035

Tool/software:

Hi expert,

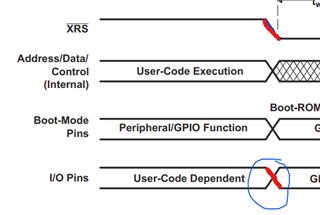

My customer want to know when the watchdog trigger the reset, at the falling edge of XRS, waht's the status of gpio?

If the pwm is high level, and the the chip reset, at the falling edge of XRS, what's the level of the pwm gpio? Is it deterministic low or uncontrolled?

Below picture is from F2800137, my customer want to know if there is any difference with F28035: Yellow channel is gpio, Green channel is pwm. When the chip is triggered reset by watchdog, the gpio fall down immediately, and the pwm is oscillating uncontrollably for 530us。

Best Regards

Anka