Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Champs,

Customer wants to use GPIO27 as the TZ signal to Epwm12, the specific method is as follows:

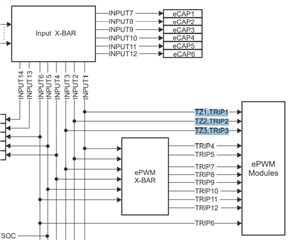

GPIO27 as the input source for InputXbar4; As shown below:

Then configure EPWMXbar:

DCxEVT is used as the trigger signal for TZ

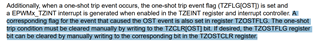

However, customer found that after they had configured it with sysconfig, they needed to set below registers, as follows:

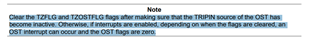

EPwm1Regs.TZCLR.all = 0x7fff; EPwm1Regs.TZOSTCLR.all = 0x00ff;

Otherwise, EPwm1Regs.TZOSTFLG.bit.DCAEVT1 will be set to 1, is this a configuration issue? Or it do need to manually clear the TZCLR after using SysConfig.

Could you help to check this? Thanks!

Julia