Other Parts Discussed in Thread: C2000WARE

Tool/software:

Hi team

Customer use DMA channel 6 to handle SPI RX buffer data, the initialization is below, SPI sent total 80 words (8 words * 10 times):

DMADest = (volatile Uint16 *)spiRecdata;

DMACH6AddrConfig(DMADest,&SpiaRegs.SPIRXBUF);

DMACH6BurstConfig(7,0,1);

DMACH6TransferConfig(9,0,1);

DMACH6ModeConfig(DMA_SPIARX,PERINT_ENABLE,ONESHOT_DISABLE,CONT_ENABLE,

SYNC_DISABLE,SYNC_SRC,OVRFLOW_DISABLE,SIXTEEN_BIT,

CHINT_END,CHINT_ENABLE);

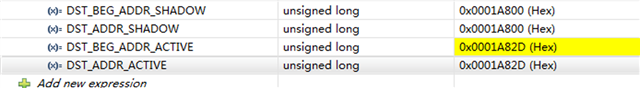

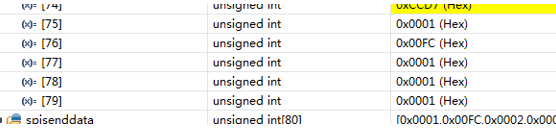

issue is the start address is not align with the setting: 0001 00FC 0001 0001 should allocated at 0x0001A800 but not in 0x001A821.

below is the debug result:

in the initialization the destination of DMA is *spiRecdata, which means spiRecdata[0].

the address is assigned in the .cmd file

TO_CPU1_INTERNALSPI : origin = 0x01A800, length = 0x000600

#pragma DATA_SECTION(spiRecdata, "tOCPU1_SPI"); // map the RX data to memory

Uint16 spiRecdata[80];

it is align with DMA ADDR_SHADOW

But in the debug DST_BEG_ADDR_ACTIVE changes randomly which leads to the destination start address moves to spiRecdata[75], but not spiRecdata[0]

is there some guidance to debug this issue?

Thanks

Joe