Part Number: LAUNCHXL-F280049C

Other Parts Discussed in Thread: C2000WARE

Tool/software:

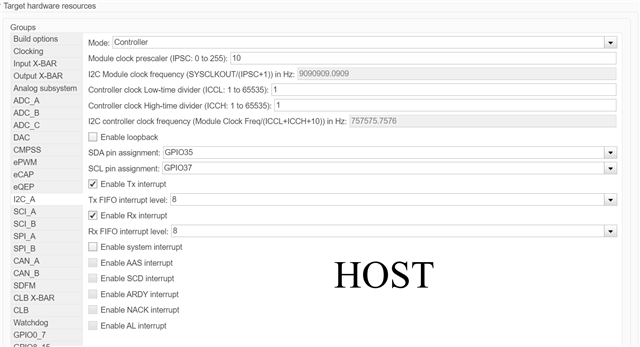

I am currently using two C2000 F280049C microcontrollers for I2C communication. One is configured as the host (master), and the other as the slave. The host microcontroller is set to transmit data, while the slave is set to receive. However, I am encountering issues where the slave is not receiving data from the host.

Interestingly, when reversing the roles (host as receiver, slave as transmitter), communication works as expected.

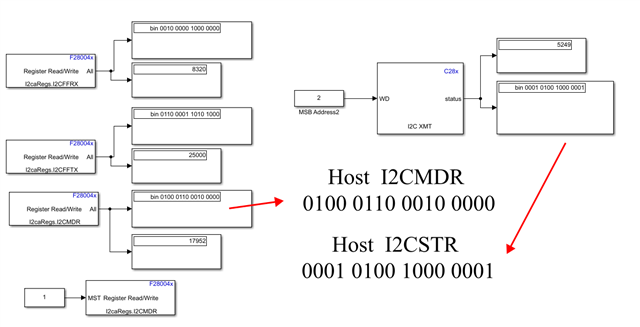

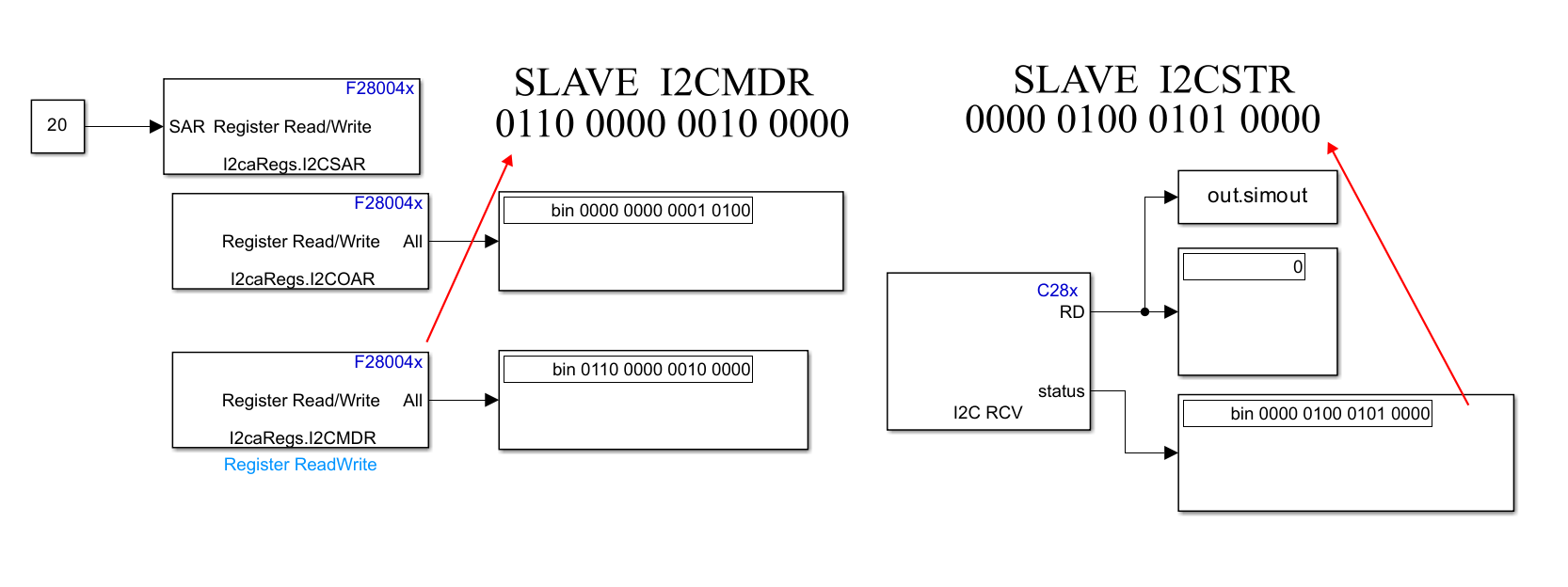

Based on the technical reference manual (SPRUI33H), the I2CMDR register is configured as follows:

Host (Master): 0x6620 (binary: 0110 0110 0010 0000)

Slave: 0x4020 (binary: 0100 0000 0010 0000)

However, the 13th bit (SST) in the I2CMDR register seems to be flipped on both microcontrollers. I tried directly writing to the registers, but the SST field does not change.

Additionally:

On the host side, the status register shows the BB (Bus Busy) and ARBL (Arbitration Lost) bits set to 1.

The slave side does not seem to receive any data.

Could you provide guidance on:

Resolving the SST bit issue in the I2CMDR register?

Clearing the BB and ARBL bits on the host?

Whether these issues are directly related to the communication failure, and if solving them would allow successful I2C data transfer?

Any assistance in troubleshooting this problem would be greatly appreciated.