Part Number: TMS320F28379D

Tool/software:

Hi Team,

I'm trying to help a customer understand how to used a shared peripheral ePWM between CPU1 and CPU2. I'm running the example DMA_ex1_shared_Periph using CCS 20.0.0.

1) I'm not sure what order to load the programs in?

I've started a projectless debug, and connected to C28xx_CPU2 and loaded dma_ex1_shared_periph_cpu2.out

I've loaded dma_ex1_shared_periph_cpu1.out into C28xx_CPU1

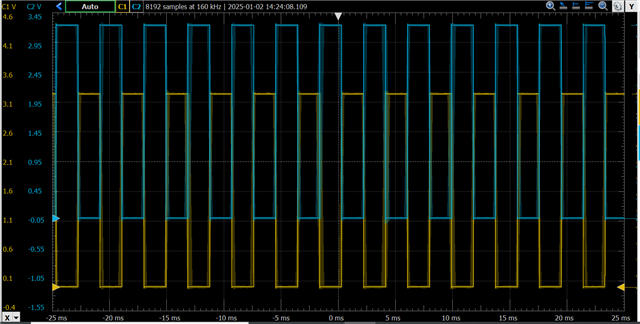

However the output I get is only a constant EPWM output as shown below:

2) Additionally, which CPU controls loading the newCMPValue into the EPWM?

I cant find a EPWM_setCounterCompareValue which calls that variable.

Thanks Team!