Other Parts Discussed in Thread: C2000WARE

Tool/software:

Hi Champ,

I am asking for my customer.

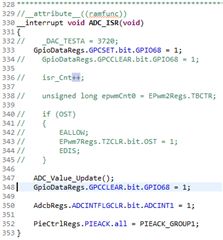

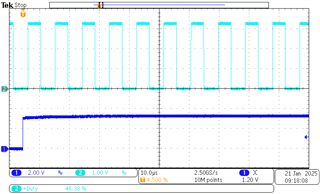

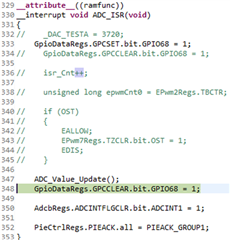

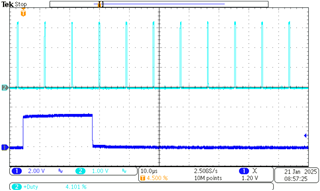

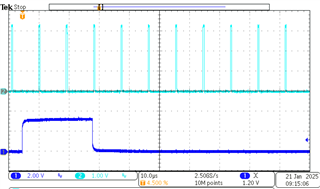

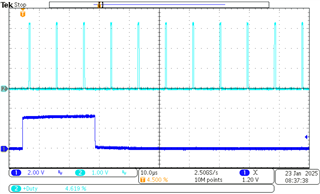

They are encountering a huge speed difference between running the piece of code (code executing on flash) in CCS debug mode and running in standalone mode by measuring with GPIO toggling. The execution time (running in debug mode / standalone) is different which is very confusing, it's supposed to be the same.

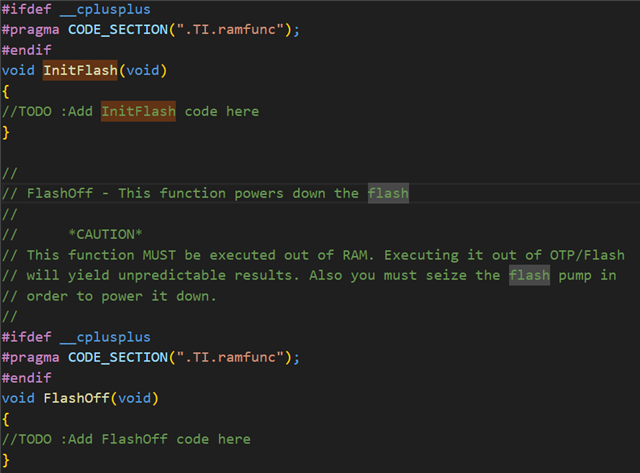

Once they move that specific piece of code to RAM (.ramfunc) with #pragma, there is no time difference in either mode respectively which is expected.

One more info is that actually it will run customer’s bootloader project first, then jump to app code. The piece of measured code is in the app code.

Asking on any ideas or suggestions why there is a time difference when running in debug mode and in standalone mode on the same piece of code ?

Thanks for the input.

Regards,

Johnny