Part Number: TMS320F28386D

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Tool/software:

Dear experts,

I am programming the CMPSS4 on the TMS320F28386D device in asynchronous mode to implement the peak current mode control.

I am not able to disable the latch in the CMPSS in order to get the asynchronous mode.

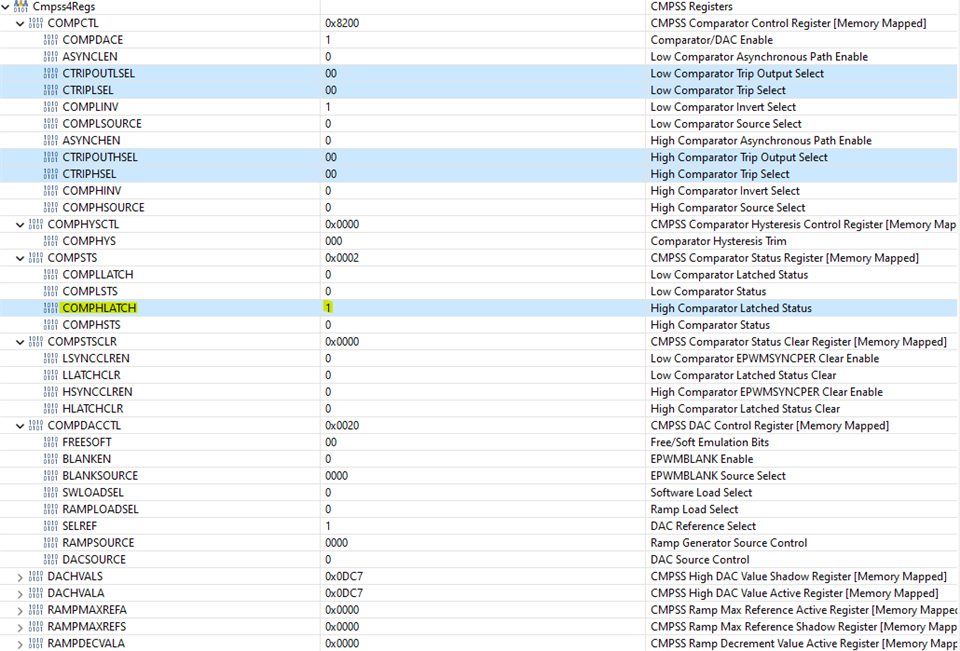

Here below the configuration of my CMPSS4

As you can see, the asynchronous path has been selected (CTRIPOUTxSEL = 0, CTRIPxSEL = 0).

Every time the analog signal overcomes the threshold, the corresponding PWM is tripped, accordingly.

However, when the analog signal decreseas up to 0, the PWM remains tripped because the output of the comparator is latched.

Finally, If i clear the bit COMPHLATCH by means of the bit HLATCHCLR, the trip of the PWM is removed.

Therefore, it seems that despite my configuration the latch is always enabled....

Why the latch of the CMPSS can not be by-passed?

Waiting for a feedback,

regards,

Benito

You should not have latched output in this case then. Also, there is CMPSS example for asynchronous trip in C2000Ware: C:\ti\c2000\C2000Ware_5_03_00_00\driverlib\f2837xs\examples\cpu1\cmpss

You should not have latched output in this case then. Also, there is CMPSS example for asynchronous trip in C2000Ware: C:\ti\c2000\C2000Ware_5_03_00_00\driverlib\f2837xs\examples\cpu1\cmpss