Other Parts Discussed in Thread: TIDM-DC-DC-BUCK, SFRA, POWERSUITE, BOOSTXL-BUCKCONV

Tool/software:

Hello,

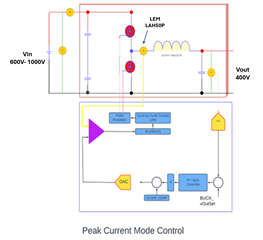

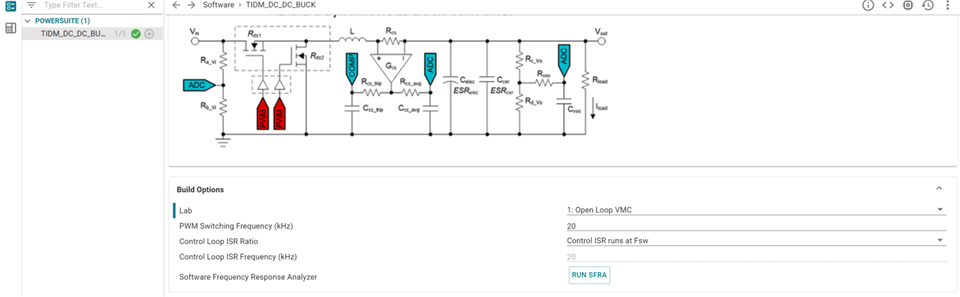

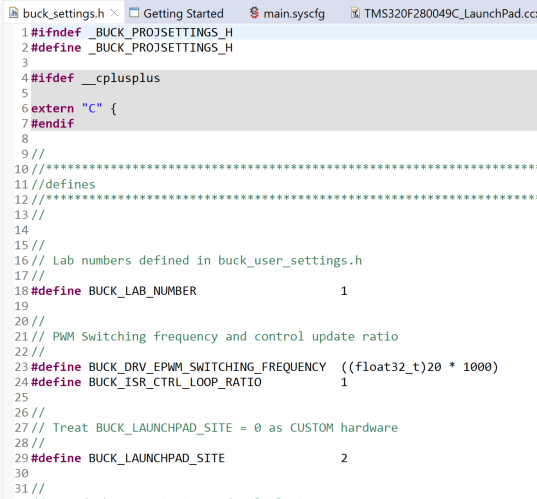

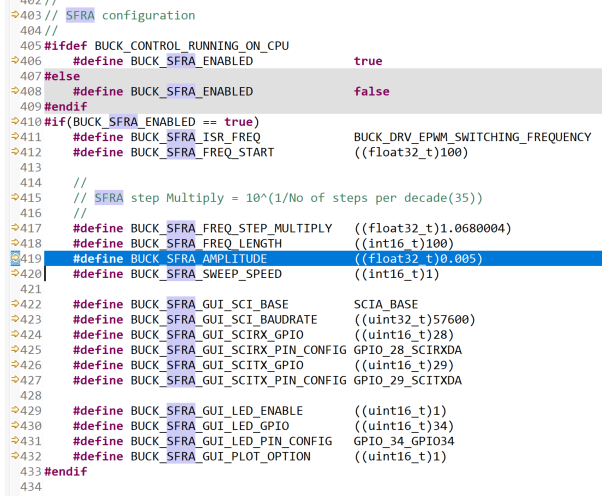

I am working on a buck converter and following the TIDM-DC-DC-BUCK firmware. While running SFRA with my 20kHz hardware setup, I observed a difference in the open-loop response in the SFRA GUI. I want to understand the discrepancy between the SFRA plot generated for the TIDM-DC-DC-BUCK kit, as shown on page 28 of the reference design user document, and the plot I obtained with my different power/voltage buck hardware at 20kHz. I have configured the TIDM-DC-DC-BUCK firmware according to the 20kHz switching frequency. According to the reference design document, the open-loop plot starts from a positive dB value, but in case of my power/voltage level hardware, it starts with a negative dB value, which conflicts with the expected buck converter open-loop response. Could you please shed some light on the missing link? If you need further information for your analysis, please let me know.

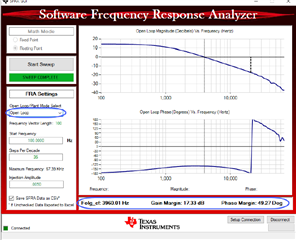

Open Loop SFRA plot for TIDM-DC-DC-BUCK-KIT (From reference manual page no. 28)

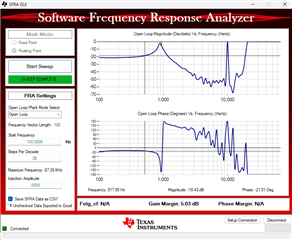

Open loop SFRA plot for my different power/voltage HW

Thanks & Regards,

Prathamesh Jadhav