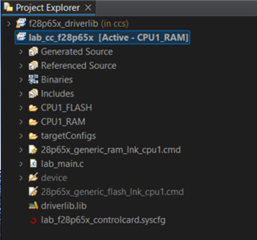

Part Number: TMS320F28P650DH

Other Parts Discussed in Thread: SYSCONFIG, TMDSCNCD28P65X

Tool/software:

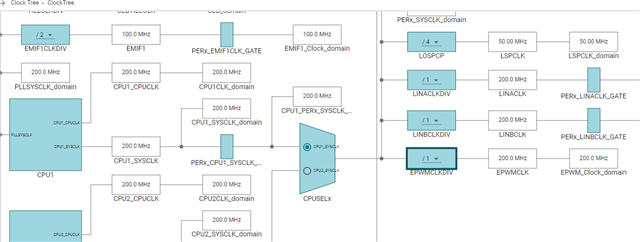

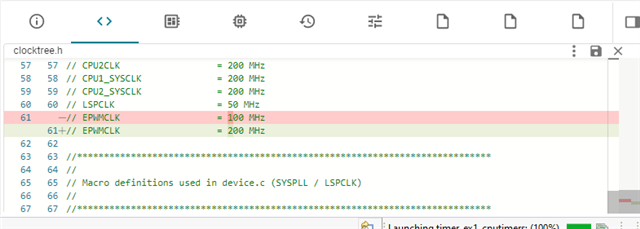

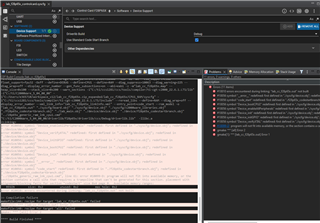

We are using CCS12.8.1. How does SysConfig ClockTree view affect the EPWMCLKDIV setting, or does it have any effect? The SysConfig ClockTree has a settable pulldown field for EPWMCLKDIV but changing this doesn't affect the EPWM clock on our board, and looking at the clocktree.h file we see that making changes to this pulldown in the GUI only changes comments in that file.

Questions:

- What is the point of having this setting within the Clocktree tool if it doesn't actually affect code generation?

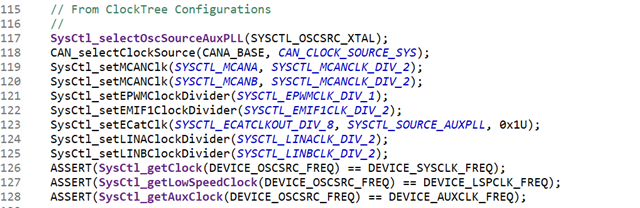

- How should one change the EPWMCLKDIV in a CCS project?