Part Number: UCC28950

Tool/software:

Hi Mike,

Continuation of a related question.

You commented that you should check the following three things as countermeasures to the oscillation phenomenon.

1. Review the capacitance of Cout

2. Set Rtmin to 10kΩ and perform testing

3. Properly set the on/off control of the SR FET

I have a question about 1.

Current Conditions

・ESR=83.33mΩ

・VTRAN=600 mV

・Pout=600 W

・Vout=12V

・Efficiency η=0.9

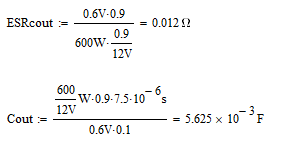

Based on the datesheet, we calculated the allowable ESR value for the output capacitor:

Calculation results : ESRCOUT≤450.54=0.012Ω=12mΩ

The current ESR value of 0.08333Ω (83.33mΩ) exceeds this limit, which may be too high. Could you please confirm if this calculation is correct?

I will also send you waveform information for your reference. Do you know the cause as shown in the attached waveform? If you find out the method to fix it, please let me know.

Full bridge waveform.xlsx

Thanks,

Conor