Other Parts Discussed in Thread: UNIFLASH, TMS320F28374S

Tool/software:

I cannot connect to TMS320F28374S using XDS110ISO-EVM debug adapter header J3. I have tried connecting with UniFlash 8.7.0.4818 and Code Composer Studio 12.8.1.

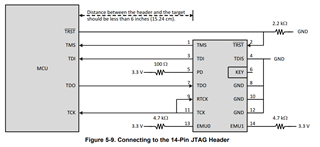

TMS320F28374S datasheet has a picture of 14-pin JTAG header where pin 2 (nTRST) is connected to MCU.

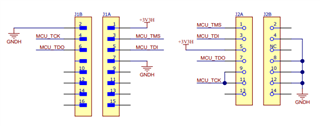

XDS110ISO-EVM schematics shows that debug adapter header J3 does not have nTRST at all. Is it needed? According to JTAG wikipage, it says nTRST is optional.

XDS110ISO-EVM package included adapter from 16-pin to 14-pin JTAG. Adapter schematics shows that nRST pin 2 in 14-pin connector is not connected.