Tool/software:

Hi experts,

I ask this for my question.

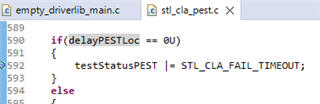

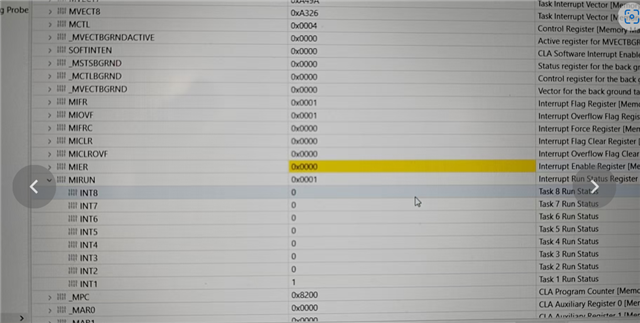

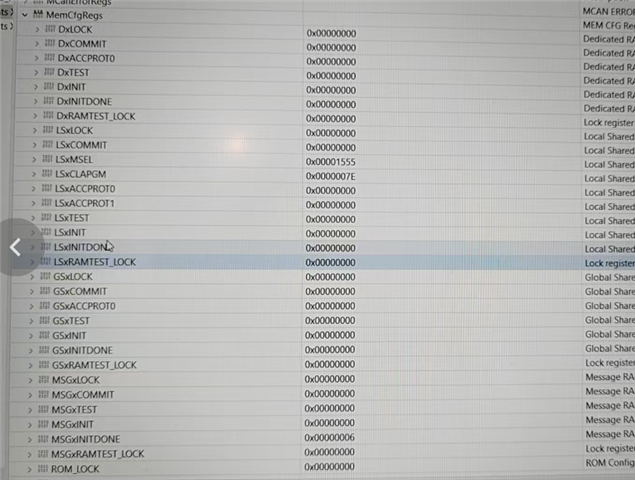

Now they have integrated CLA_STL into their application, and STL_CLA_testRegisters1(), STL_CLA_testRegisters2(), STL_CLA_testRegisters3(), STL_CLA_runPOSTMicro(), STL_CLA_runPESTMicro() pass, but the STL_CLA_ALL() failed, the returnVal is 1; I checked their cmd:

//---------------------------------------------------------------------------------------------------------------------

//

// \file STA_F28003x_FLASH_CLASWBIST.cmd

//

// \brief The file defines the LOAD address (Start address, length and End address) and RUN address for the

// test groups supported by the C28x_STL.

//

// \References: 1. http://www.ti.com/lit/pdf/spru513 - TMS320C28x Assembly Language Tools

//

// \note 1. Required to ensure that each of the test vectors are exported from the library to make them

// linkable.

// As seen the in the examples sections (defined in stl_claswbist_s.asm) below from the map file:

// STL_CLA_postVect00 00008000 00000000 UNINITIALIZED

// STL_CLA_postVect01 00008000 00000000 UNINITIALIZED

// The --undef_sym option introduces the linkname for an unresolved symbol into the linker's

// symbol table. This forces the linker to search a library and include the member that defines the

// symbol. The linker must encounter the --undef_sym option before it links in the member that defines

// the symbol. See Reference listed above for further details.

// With the symbol "exportFromLibrary" defined the example sections described above are defined:

// STL_CLA_postVect00

// * 0 00011d90 00000028 RUN ADDR = 00008000

// 00011d90 00000028 F28003x_CLA_STL_RELEASE.lib : stl_claswbist_s.obj (STL_CLA_postVect00)

// STL_CLA_postVect01

// * 0 00011a7c 0000004a RUN ADDR = 00008000

// 00011a7c 0000004a F28003x_CLA_STL_RELEASE.lib : stl_claswbist_s.obj (STL_CLA_postVect01)

//

//---------------------------------------------------------------------------------------------------------------------

//---------------------------------------------------------------------------------------------------------------------

// VERSION HISTORY

//---------------------------------------------------------------------------------------------------------------------

// DATE AUTHOR(ID) JIRA ID Description

//---------------------------------------------------------------------------------------------------------------------

// 04/16/2020 a0322200 C2000DL-144 CLA_STL: Comprehend and evaluate customer feedback, Address following:

// - TI will check stl-cla-lib to have included the stl_claswbist_s.asm

//---------------------------------------------------------------------------------------------------------------------

--undef_sym=exportFromLibrary // See Note 1 above

SECTIONS

{

UNION: 0x8000 PAGE = 1

{

STL_CLA_postVect00 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE=0

LOAD_START(postVect00LoadStart),

LOAD_SIZE(postVect00LoadSize),

LOAD_END(postVect00LoadEnd)

STL_CLA_postVect01 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE=0

LOAD_START(postVect01LoadStart),

LOAD_SIZE(postVect01LoadSize),

LOAD_END(postVect01LoadEnd)

STL_CLA_postVect02 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE=0

LOAD_START(postVect02LoadStart),

LOAD_SIZE(postVect02LoadSize),

LOAD_END(postVect02LoadEnd)

STL_CLA_postVect03 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE=0

LOAD_START(postVect03LoadStart),

LOAD_SIZE(postVect03LoadSize),

LOAD_END(postVect03LoadEnd)

STL_CLA_postVect04 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE=0

LOAD_START(postVect04LoadStart),

LOAD_SIZE(postVect04LoadSize),

LOAD_END(postVect04LoadEnd)

STL_CLA_postVect05_08 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(postVect05_08LoadStart),

LOAD_SIZE(postVect05_08LoadSize),

LOAD_END(postVect05_08LoadEnd)

STL_CLA_postVect06 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(postVect06LoadStart),

LOAD_SIZE(postVect06LoadSize),

LOAD_END(postVect06LoadEnd)

STL_CLA_postVect07 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(postVect07LoadStart),

LOAD_SIZE(postVect07LoadSize),

LOAD_END(postVect07LoadEnd)

STL_CLA_postVect09 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(postVect09LoadStart),

LOAD_SIZE(postVect09LoadSize),

LOAD_END(postVect09LoadEnd)

STL_CLA_postVect10 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(postVect10LoadStart),

LOAD_SIZE(postVect10LoadSize),

LOAD_END(postVect10LoadEnd)

STL_CLA_postVect11 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(postVect11LoadStart),

LOAD_SIZE(postVect11LoadSize),

LOAD_END(postVect11LoadEnd)

STL_CLA_pestVect01 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect01LoadStart),

LOAD_SIZE(pestVect01LoadSize),

LOAD_END(pestVect01LoadEnd)

STL_CLA_pestVect02 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect02LoadStart),

LOAD_SIZE(pestVect02LoadSize),

LOAD_END(pestVect02LoadEnd)

STL_CLA_pestVect03 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect03LoadStart),

LOAD_SIZE(pestVect03LoadSize),

LOAD_END(pestVect03LoadEnd)

STL_CLA_pestVect04 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect04LoadStart),

LOAD_SIZE(pestVect04LoadSize),

LOAD_END(pestVect04LoadEnd)

STL_CLA_pestVect05 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect05LoadStart),

LOAD_SIZE(pestVect05LoadSize),

LOAD_END(pestVect05LoadEnd)

STL_CLA_pestVect06 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect06LoadStart),

LOAD_SIZE(pestVect06LoadSize),

LOAD_END(pestVect06LoadEnd)

STL_CLA_pestVect07 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect07LoadStart),

LOAD_SIZE(pestVect07LoadSize),

LOAD_END(pestVect07LoadEnd)

STL_CLA_pestVect08 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect08LoadStart),

LOAD_SIZE(pestVect08LoadSize),

LOAD_END(pestVect08LoadEnd)

STL_CLA_pestVect09 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect09LoadStart),

LOAD_SIZE(pestVect09LoadSize),

LOAD_END(pestVect09LoadEnd)

STL_CLA_pestVect10 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect10LoadStart),

LOAD_SIZE(pestVect10LoadSize),

LOAD_END(pestVect10LoadEnd)

STL_CLA_pestVect11 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect11LoadStart),

LOAD_SIZE(pestVect11LoadSize),

LOAD_END(pestVect11LoadEnd)

STL_CLA_pestVect12 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect12LoadStart),

LOAD_SIZE(pestVect12LoadSize),

LOAD_END(pestVect12LoadEnd)

STL_CLA_pestVect13 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect13LoadStart),

LOAD_SIZE(pestVect13LoadSize),

LOAD_END(pestVect13LoadEnd)

STL_CLA_pestVect14 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect14LoadStart),

LOAD_SIZE(pestVect14LoadSize),

LOAD_END(pestVect14LoadEnd)

STL_CLA_pestVect15 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect15LoadStart),

LOAD_SIZE(pestVect15LoadSize),

LOAD_END(pestVect15LoadEnd)

STL_CLA_pestVect16 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect16LoadStart),

LOAD_SIZE(pestVect16LoadSize),

LOAD_END(pestVect16LoadEnd)

STL_CLA_pestVect17 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect17LoadStart),

LOAD_SIZE(pestVect17LoadSize),

LOAD_END(pestVect17LoadEnd)

STL_CLA_pestVect18 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect18LoadStart),

LOAD_SIZE(pestVect18LoadSize),

LOAD_END(pestVect18LoadEnd)

STL_CLA_pestVect19 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect19LoadStart),

LOAD_SIZE(pestVect19LoadSize),

LOAD_END(pestVect19LoadEnd)

STL_CLA_pestVect20 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect20LoadStart),

LOAD_SIZE(pestVect20LoadSize),

LOAD_END(pestVect20LoadEnd)

STL_CLA_pestVect21 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect21LoadStart),

LOAD_SIZE(pestVect21LoadSize),

LOAD_END(pestVect21LoadEnd)

STL_CLA_pestVect22 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect22LoadStart),

LOAD_SIZE(pestVect22LoadSize),

LOAD_END(pestVect22LoadEnd)

STL_CLA_pestVect23 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect23LoadStart),

LOAD_SIZE(pestVect23LoadSize),

LOAD_END(pestVect23LoadEnd)

STL_CLA_pestVect24 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect24LoadStart),

LOAD_SIZE(pestVect24LoadSize),

LOAD_END(pestVect24LoadEnd)

STL_CLA_pestVect25 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect25LoadStart),

LOAD_SIZE(pestVect25LoadSize),

LOAD_END(pestVect25LoadEnd)

STL_CLA_pestVect26 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect26LoadStart),

LOAD_SIZE(pestVect26LoadSize),

LOAD_END(pestVect26LoadEnd)

STL_CLA_pestVect27 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect27LoadStart),

LOAD_SIZE(pestVect27LoadSize),

LOAD_END(pestVect27LoadEnd)

STL_CLA_pestVect28 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect28LoadStart),

LOAD_SIZE(pestVect28LoadSize),

LOAD_END(pestVect28LoadEnd)

STL_CLA_pestVect29 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect29LoadStart),

LOAD_SIZE(pestVect29LoadSize),

LOAD_END(pestVect29LoadEnd)

STL_CLA_pestVect30 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect30LoadStart),

LOAD_SIZE(pestVect30LoadSize),

LOAD_END(pestVect30LoadEnd)

STL_CLA_pestVect31 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect31LoadStart),

LOAD_SIZE(pestVect31LoadSize),

LOAD_END(pestVect31LoadEnd)

STL_CLA_pestVect32 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect32LoadStart),

LOAD_SIZE(pestVect32LoadSize),

LOAD_END(pestVect32LoadEnd)

STL_CLA_pestVect33 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect33LoadStart),

LOAD_SIZE(pestVect33LoadSize),

LOAD_END(pestVect33LoadEnd)

STL_CLA_pestVect34 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect34LoadStart),

LOAD_SIZE(pestVect34LoadSize),

LOAD_END(pestVect34LoadEnd)

STL_CLA_pestVect35 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect35LoadStart),

LOAD_SIZE(pestVect35LoadSize),

LOAD_END(pestVect35LoadEnd)

STL_CLA_pestVect36 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect36LoadStart),

LOAD_SIZE(pestVect36LoadSize),

LOAD_END(pestVect36LoadEnd)

STL_CLA_pestVect37 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect37LoadStart),

LOAD_SIZE(pestVect37LoadSize),

LOAD_END(pestVect37LoadEnd)

STL_CLA_pestVect38 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect38LoadStart),

LOAD_SIZE(pestVect38LoadSize),

LOAD_END(pestVect38LoadEnd)

STL_CLA_pestVect39 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect39LoadStart),

LOAD_SIZE(pestVect39LoadSize),

LOAD_END(pestVect39LoadEnd)

STL_CLA_pestVect40 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect40LoadStart),

LOAD_SIZE(pestVect40LoadSize),

LOAD_END(pestVect40LoadEnd)

STL_CLA_pestVect41 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect41LoadStart),

LOAD_SIZE(pestVect41LoadSize),

LOAD_END(pestVect41LoadEnd)

STL_CLA_pestVect42 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect42LoadStart),

LOAD_SIZE(pestVect42LoadSize),

LOAD_END(pestVect42LoadEnd)

STL_CLA_pestVect43 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect43LoadStart),

LOAD_SIZE(pestVect43LoadSize),

LOAD_END(pestVect43LoadEnd)

STL_CLA_pestVect44 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect44LoadStart),

LOAD_SIZE(pestVect44LoadSize),

LOAD_END(pestVect44LoadEnd)

STL_CLA_pestVect45 :

LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6, PAGE = 0

LOAD_START(pestVect45LoadStart),

LOAD_SIZE(pestVect45LoadSize),

LOAD_END(pestVect45LoadEnd)

}

STL_CLA_postVect03Return1 : LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6,

LOAD_START(postVect03Return1LoadStart),

LOAD_SIZE(postVect03Return1LoadSize),

LOAD_END(postVect03Return1LoadEnd),

RUN = 0x00AF90,

PAGE = 0

STL_CLA_postVect03Return2 : LOAD = FLASH_BANK0_SEC5 | FLASH_BANK0_SEC6,

LOAD_START(postVect03Return2LoadStart),

LOAD_SIZE(postVect03Return2LoadSize),

LOAD_END(postVect03Return2LoadEnd),

RUN = 0x00AFD4,

PAGE = 0

}

//---------------------------------------------------------------------------------------------------------------------

// End of File

//---------------------------------------------------------------------------------------------------------------------

//---------------------------------------------------------------------------------------------------------------------

// The user must define CLA_C in the project linker settings if using the CLA C compiler as follows:

// Project Properties -> C2000 Linker -> Advanced Options -> Command File Preprocessing -> --define

//---------------------------------------------------------------------------------------------------------------------

#ifdef CLA_C

// Define a size for the CLA scratchpad area that will be used by the CLA compiler for local symbols and temps

// Also force references to the special symbols that mark the scratchpad are.

CLA_SCRATCHPAD_SIZE = 0x100;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

#endif // CLA_C

MEMORY

{

PAGE 0 :

// BEGIN is used for the "boot to SARAM" bootloader mode

HWBIST : origin = 0x000000, length = 0x000020

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x0000F5, length = 0x00030B

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000790

RAMLS5_end1 : origin = 0x00AF90, length = 0x000044

RAMLS5_end2 : origin = 0x00AFD4, length = 0x00002C

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x002000

RAMGS1 : origin = 0x00E000, length = 0x002000

RAMGS2 : origin = 0x010000, length = 0x002000

RAMGS3 : origin = 0x012000, length = 0x002000

RESET : origin = 0x3FFFC0, length = 0x000002

// Flash sectors

// BANK 0

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE // on-chip Flash

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 // on-chip Flash

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x001000 // on-chip Flash

// BANK 1

FLASH_BANK1_SEC0 : origin = 0x090000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC1 : origin = 0x091000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC2 : origin = 0x092000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC3 : origin = 0x093000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC4 : origin = 0x094000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC5 : origin = 0x095000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC6 : origin = 0x096000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC7 : origin = 0x097000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC8 : origin = 0x098000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC9 : origin = 0x099000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC10 : origin = 0x09A000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC11 : origin = 0x09B000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC12 : origin = 0x09C000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC13 : origin = 0x09D000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC14 : origin = 0x09E000, length = 0x001000 // on-chip Flash

FLASH_BANK1_SEC15 : origin = 0x09F000, length = 0x001000 // on-chip Flash

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x0000F3 // Part of M0, BOOT rom will use this for stack

RAMM1 : origin = 0x000400, length = 0x000400 // on-chip RAM block M1

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

}

SECTIONS

{

// Allocate program areas:

.cinit : > FLASH_BANK0_SEC4, PAGE = 0, ALIGN(4)

.init_array : > FLASH_BANK0_SEC4, PAGE = 0, ALIGN(4)

.text : >> FLASH_BANK0_SEC0 | FLASH_BANK0_SEC1 | FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3, PAGE = 0, ALIGN(4)

codestart : > BEGIN PAGE = 0, ALIGN(4)

.TI.ramfunc : {} LOAD = FLASH_BANK0_SEC4,

RUN = RAMLS4,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

// Allocate uninitalized data sections:

.stack : > RAMM1 PAGE = 1

.bss : > RAMGS0 PAGE = 0

.sysmem : > RAMGS0 PAGE = 0

.data : > RAMLS3 PAGE = 1

// Initalized sections go in Flash

.const : > FLASH_BANK0_SEC4 PAGE = 0, ALIGN(4)

.switch : > FLASH_BANK0_SEC4 PAGE = 0, ALIGN(4)

// not used

.reset : > RESET, PAGE = 0, TYPE = DSECT

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

#ifdef CLA_C

// CLA C compiler sections

// Must be allocated to memory the CLA has write access to

CLAscratch :

{ *.obj(CLAscratch) . += CLA_SCRATCHPAD_SIZE; *.obj(CLAscratch_end) } > RAMLS1, PAGE = 1

.scratchpad : > RAMLS1, PAGE = 1

.bss_cla : > RAMLS1, PAGE = 1

.const_cla : LOAD = FLASH_BANK0_SEC4,

RUN = RAMLS1,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

PAGE = 1

#endif // CLA_C

}

//---------------------------------------------------------------------------------------------------------------------

// End of File

//---------------------------------------------------------------------------------------------------------------------

They don't change the source code of CAL_STL, and the code is show:

/**

* \file Fusa_Cpu.c

* \author Yang Zuqiao

* \brief Source file for fusa CAN Loop Back

* \copyright (c) 2024 Preh GmbH, all rights reserved.

*/

/*----------------------------------------------------------------------------*/

/* Includes */

/*----------------------------------------------------------------------------*/

#include "Fusa_Cpu.h"

#include "hw_memmap.h"

#include "hw_pie.h"

#include "stdlib.h"

#include "sta_util.h"

/*----------------------------------------------------------------------------*/

/* Micro Define */

/*----------------------------------------------------------------------------*/

/*----------------------------------------------------------------------------*/

/* Definition of RAM-Variables */

/*----------------------------------------------------------------------------*/

const STA_Tests_Types STA_Tests_testArray[STA_TESTS_NUMBERS] =

{

STA_CLA_TEST_START,

STA_CLA_TEST_REGISTERS_1,

STA_CLA_TEST_REGISTERS_2,

STA_CLA_TEST_REGISTERS_3,

STA_CLA_POST,

STA_CLA_PEST,

STA_CLA_ALL,

STA_CLA_TEST_END

};

uint16 numPOST = 0;

uint16 numPEST = 0;

uint16 enableErrorInject = 0;

uint16 test_1 = 0;

/*----------------------------------------------------------------------------*/

/* Local data at RAM */

/*----------------------------------------------------------------------------*/

static boolean STA_Tests_injectError = 0U;

static uint16 STA_Tests_passCount = 0U;

static boolean STA_Tests_report[10] = {0};

/*----------------------------------------------------------------------------*/

/* Declaration of local functions */

/*----------------------------------------------------------------------------*/

static uint16 STA_Tests_testDevice(STA_Tests_Types testItem);

/*----------------------------------------------------------------------------*/

/* Implementation of global functions */

/*----------------------------------------------------------------------------*/

uint8 FusaStl_StartupCheck(void)

{

uint16 returnVal = E_NOT_OK;

STA_Tests_Types i = STA_CLA_TEST_START;

for(i = STA_CLA_TEST_START; i <= STA_CLA_TEST_END; i++)

{

returnVal |= STA_Tests_testDevice(i);

}

test_1 = returnVal;

return returnVal;

}

/*----------------------------------------------------------------------------*/

/* Implementation of local functions */

/*---------------------------------------static-------------------------------------*/

static uint16 STA_Tests_testDevice(STA_Tests_Types testItem)

{

uint16 returnVal = E_NOT_OK;

switch(testItem)

{

case STA_CLA_TEST_START:

{

//

// Configure the CLA memory one time.

//

STL_CLA_configMemory();

STA_Tests_report[0] = 1;

STA_Tests_passCount = 0U;

break;

}

case STA_CLA_TEST_REGISTERS_1:

{

uint32 claBase = CLA1_BASE;

if(STA_Tests_injectError)

{

claBase = ADCARESULT_BASE;

}

returnVal = STL_CLA_testRegisters1(claBase);

if(STL_CLA_PASS == returnVal)

{

STA_Tests_passCount++;

STA_Tests_report[1] = 0;

}

else

{

STA_Tests_report[1] = 1;

}

break;

}

case STA_CLA_TEST_REGISTERS_2:

{

uint32 claBase = CLA1_BASE;

if(STA_Tests_injectError)

{

claBase = ADCARESULT_BASE;

}

returnVal = STL_CLA_testRegisters2(claBase);

if(STL_CLA_PASS == returnVal)

{

STA_Tests_passCount++;

STA_Tests_report[2] = 0;

}

else

{

STA_Tests_report[2] = 1;

}

break;

}

case STA_CLA_TEST_REGISTERS_3:

{

uint16 delay = 50U;

uint32 claBase = CLA1_BASE;

if(STA_Tests_injectError)

{

claBase = ADCARESULT_BASE;

}

//

// Clear task complete flag in PIE.

//

(*((volatile uint16 *)(PIECTRL_BASE + PIE_O_IFR11))) = 0x0000U;

returnVal = STL_CLA_testRegisters3(claBase, delay);

if(STL_CLA_PASS == returnVal)

{

STA_Tests_passCount++;

STA_Tests_report[3] = 0;

}

else

{

STA_Tests_report[3] = 1;

}

break;

}

case STA_CLA_POST:

{

uint16 delay = 50U;

if(STA_Tests_injectError)

{

delay = 2U;

}

//

// Clear task complete flag in PIE.

//

(*((volatile uint16 *)(PIECTRL_BASE + PIE_O_IFR11))) = 0x0000U;

//

// Copy test segment to RAMLS0 for CLA execution.

//

STL_CLA_bootVector((uint32 *)STL_CLA_postHandleArray[numPOST]->vectorAddress, \

(size_t)STL_CLA_postHandleArray[numPOST]->vectorLength);

//

// Run a micro-run of CLASWBIST.

//

for(numPOST = 0; numPOST < STL_CLA_POST_NUM_VECTS; numPOST++)

{

returnVal |= STL_CLA_runPOSTMicro((STL_CLA_POSTVector)numPOST, delay);

}

if(STL_CLA_PASS == returnVal)

{

STA_Tests_passCount++;

STA_Tests_report[4] = 0;

}

else

{

STA_Tests_report[4] = 1;

}

break;

}

case STA_CLA_PEST:

{

uint16 delay = 50U;

if(STA_Tests_injectError)

{

delay = 2U;

}

//

// Clear task complete flag in PIE.

//

(*((volatile uint16 *)(PIECTRL_BASE + PIE_O_IFR11))) = 0x0000U;

//

// Copy test segment to RAMLS0 for CLA execution.

//

STL_CLA_bootVector((uint32 *)STL_CLA_pestHandleArray[numPEST]->vectorAddress, \

(size_t)STL_CLA_pestHandleArray[numPEST]->vectorLength);

//

// TID_02_73_01

//

//

// Run a micro-run of CLASWBIST.

//

for(numPEST = 0; numPEST < STL_CLA_PEST_NUM_VECTS; numPEST++)

{

returnVal |= STL_CLA_runPESTMicro((STL_CLA_PESTVector)numPEST, delay);

}

returnVal = STL_CLA_runPESTMicro(STL_CLA_PEST_VECTOR_02, delay);

if(STL_CLA_PASS == returnVal)

{

STA_Tests_passCount++;

STA_Tests_report[5] = 0;

}

else

{

STA_Tests_report[5] = 1;

}

break;

}

case STA_CLA_ALL:

{

uint16 delay = 50U;

uint32 claBase = CLA1_BASE;

uint16 returnVal = STL_CLA_PASS;

sint16 numPOSTAll;

sint16 numPESTAll;

if(STA_Tests_injectError)

{

claBase = 0x80000UL;

delay = 2U;

}

//

// TID_02_74_01

//

//

// Copy test segment to RAMLS0 for CLA execution.

//

//

// POST tests

//

returnVal |= STL_CLA_testRegisters1(claBase);

returnVal |= STL_CLA_testRegisters2(claBase);

returnVal |= STL_CLA_testRegisters3(claBase, delay);

STA_Tests_report[6] = returnVal;

for(numPOSTAll = 0; numPOSTAll < STL_CLA_POST_NUM_VECTS; numPOSTAll++)

{

STL_CLA_bootVector((uint32 *)STL_CLA_postHandleArray[numPOSTAll]->vectorAddress, \

(size_t)STL_CLA_postHandleArray[numPOSTAll]->vectorLength);

if ((STL_CLA_POST_VECTOR_11 == numPOSTAll) && (FALSE == STA_Tests_injectError))

{

delay = STL_CLA_FPU_TEST_DELAY; // POST vector 11 - FPU tests - POST only cannot qualify for PEST

}

returnVal |= STL_CLA_runPOSTMicro((STL_CLA_POSTVector)numPOSTAll, delay);

STA_Tests_report[7] = STL_CLA_runPOSTMicro((STL_CLA_POSTVector)numPOSTAll, delay);

}

//

// PEST tests

//

if(STL_CLA_PASS == returnVal)

{

for(numPESTAll = 0; numPESTAll < STL_CLA_PEST_NUM_VECTS; numPESTAll++)

{

STL_CLA_bootVector((uint32 *)STL_CLA_pestHandleArray[numPESTAll]->vectorAddress, \

(size_t)STL_CLA_pestHandleArray[numPESTAll]->vectorLength);

returnVal |= STL_CLA_runPESTMicro((STL_CLA_PESTVector)numPESTAll, delay);

STA_Tests_report[8] = STL_CLA_runPESTMicro((STL_CLA_PESTVector)numPESTAll, delay);

}

}

if(STL_CLA_PASS == returnVal)

{

STA_Tests_passCount++;

STA_Tests_report[9] = 0;

}

else

{

STA_Tests_report[9] = 1;

}

break;

}

case STA_CLA_TEST_END:

{

STA_Tests_report[7] = 1;

break;

}

default:

{

break;

}

}

return returnVal;

}

/**

* \file Fusa_Cpu.h

* \author Yang Zuqiao

* \brief Header file for fusa CAN Loop Back

* \copyright (c) 2024 Preh GmbH, all rights reserved.

*/

#ifndef FUSA_CPU_H

#define FUSA_CPU_H

/*----------------------------------------------------------------------------*/

/* Includes */

/*----------------------------------------------------------------------------*/

#include "Std_Types.h"

#include "stl_cla.h"

/*----------------------------------------------------------------------------*/

/* Micro Define */

/*----------------------------------------------------------------------------*/

#define STA_TESTS_NUMBERS 8U

#define STA_TESTS_PASS 0U

#define STA_TESTS_FAIL 1U

/*----------------------------------------------------------------------------*/

/* Data types */

/*----------------------------------------------------------------------------*/

typedef enum

{

STA_CLA_TEST_START, //!< Designates beginning of new series of tests

STA_CLA_TEST_REGISTERS_1, //!< POST test STL_CLA_testRegisters1()

STA_CLA_TEST_REGISTERS_2, //!< POST test STL_CLA_testRegisters2()

STA_CLA_TEST_REGISTERS_3, //!< POST test STL_CLA_testRegisters3()

STA_CLA_POST, //!< POST test STL_CLA_runPOSTMicro()

STA_CLA_PEST, //!< PEST test STL_CLA_runPESTMicro()

STA_CLA_ALL, //!< Full execution of CLA STL (>=90% DC)

STA_CLA_TEST_END //!< Designates the end of series of tests

} STA_Tests_Types;

/*----------------------------------------------------------------------------*/

/* Declaration of global functions */

/*----------------------------------------------------------------------------*/

extern uint8 FusaStl_StartupCheck(void);

#endif /* FUSA_CPU_H */

1. Do you give some advice why the all test is fail?

2. In STL_CLA_ALL test, it includes STL_CLA_testRegisters1(), STL_CLA_testRegisters2(), STL_CLA_testRegisters3(), STL_CLA_runPOSTMicro(), STL_CLA_runPESTMicro() that have been tested, why it need to run the STL_CLA_ALL test? Is any difference between the above test?

3. I noticed that in our user guide, it shows the CLA_STL is intended to be part of embedded application, so I want to double confirm that CLA_TEST needed to be run in a loop, and customer can't just run it in the initialization?

BRs

Shuqing