Other Parts Discussed in Thread: C2000WARE

Tool/software:

We have trouble on using ePWM and CMPSS.

Explanation is below.

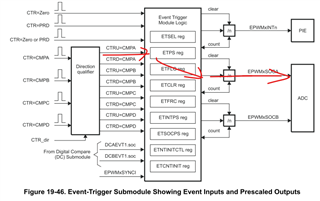

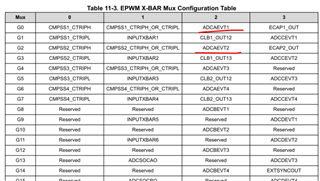

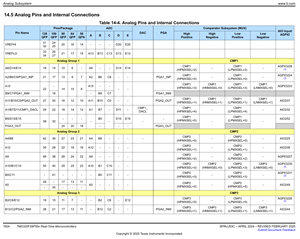

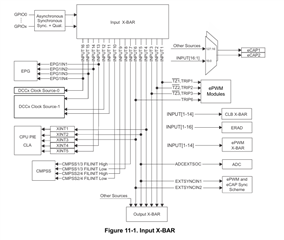

ePWMx changes high/low several reason(DCVEVT, CMPx).

So we should watch real output, and reset CMPSS ramp on edges of outputs.

Is there any solution?

Best regards.