Tool/software:

Hello,

I am working on the F28379D and trying to route the XCLKOUT signal to an accessible GPIO pin using the XBAR fabric.

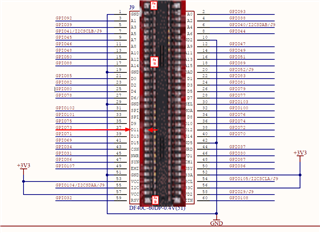

Since GPIO73 is configured for XCLKOUT, but not physically probe-able on my board, I tried the following routing:

XCLKOUT (via GPIO73) → InputXBAR1 → OutputXBAR1 → GPIO24

Below is the code I used (simplified):

#include "F2837xD_sysctrl.h"

#include "F2837xD_gpio.h"

#include "F2837xD_xbar.h"

void led(void);

void main(void) {

// Configure XCLKOUT source and divider

EALLOW; //

ClkCfgRegs.CLKSRCCTL1.bit.XTALOFF = 0; // Enable XTAL

ClkCfgRegs.CLKSRCCTL3.bit.XCLKOUTSEL = 2; // CPU2.sysclk as source

ClkCfgRegs.XCLKOUTDIVSEL.bit.XCLKOUTDIV = 1; // Divide by 2

GpioCtrlRegs.GPAGMUX1.bit.GPIO1 = 0;

GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 0;

GpioCtrlRegs.GPADIR.bit.GPIO1 = 1;

GpioDataRegs.GPACLEAR.bit.GPIO1 = 0;

GpioCtrlRegs.GPAGMUX2.bit.GPIO16 = 0;

GpioCtrlRegs.GPAMUX2.bit.GPIO16 = 0;

GpioCtrlRegs.GPADIR.bit.GPIO16 = 0;

GpioCtrlRegs.GPAPUD.bit.GPIO16 = 1;

GpioCtrlRegs.GPCGMUX1.bit.GPIO73 = 1;

GpioCtrlRegs.GPCMUX1.bit.GPIO73 = 3;

GpioCtrlRegs.GPCDIR.bit.GPIO73 = 1;

// Configure Input XBAR to route GPIO73 (XCLKOUT)

InputXbarRegs.INPUTSELECTLOCK.bit.INPUT1SELECT = 0; // Unlock Input Select

InputXbarRegs.INPUT1SELECT = 73; // Route GPIO73 (49 in hexa) to InputXBAR1

InputXbarRegs.INPUTSELECTLOCK.bit.INPUT1SELECT = 1;

// Configure Output XBAR to route InputXBAR1 to GPIO24

OutputXbarRegs.OUTPUTLOCK.bit.LOCK = 0; // Unlock Output Select

OutputXbarRegs.OUTPUT1MUX0TO15CFG.bit.MUX1 = 1; // Route InputXBAR1 to MUX1 of Output1

OutputXbarRegs.OUTPUT1MUXENABLE.bit.MUX1 = 1;

OutputXbarRegs.OUTPUTLATCHENABLE.bit.OUTPUT1 = 0;

OutputXbarRegs.OUTPUTINV.bit.OUTPUT1 = 0;

// Configure GPIO24 for OutputXBAR function

GpioCtrlRegs.GPAGMUX2.bit.GPIO24 = 1;

GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 1; //select as OUTPUTXBAR1

GpioCtrlRegs.GPADIR.bit.GPIO24 = 1; // Set as output

EDIS;

while(1)

{

led(); //just to check whether program is working

}

}

void led()

{

if (GpioDataRegs.GPADAT.bit.GPIO16 == 0) {

// Button is pressed (LOW), turn on the LED

GpioDataRegs.GPASET.bit.GPIO1 = 1;

} else {

// Button is not pressed (HIGH), turn off the LED

GpioDataRegs.GPACLEAR.bit.GPIO1 = 1;

}

}

-

The LED responds correctly to the button, which confirms the program is running.

-

All related registers (checked via Expressions window) are correctly set.

-

However, when I probe GPIO24 on the oscilloscope (with and without EDU MKII), I only see noise—no square wave or clock signal.

-

I’ve tried adjusting the XCLKOUT source and divider but still no signal is seen.

Question:

Why is the signal not reaching GPIO24? Is the InputXBAR1 → OutputXBAR1 routing valid for this purpose, or am I missing something?

Any insights would be greatly appreciated!

Thank you,

Shivani