Tool/software:

Good morning

This might end up being more appropriate for the compiler forum, but let's start here. I am doing some analysis on the context save which happens upon entering an interrupt service routine written in C and referencing a value on the stack.

What I have found is that the context save which is done by the C28x seemingly varies depending on the contents of the ISR. I have spent a fair amount of time reading about the context save and restores in the assembly manual, but I haven't found anything specific to this in the context of when executing the ISR in C.

Here are two examples of the disassembly:

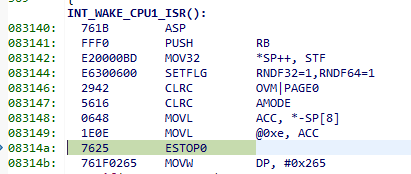

The first is a very short version of a watchdog ISR which basically reads a value off of the stack, checks if it should reset the CPU, and acknowledges the interrupt flag.

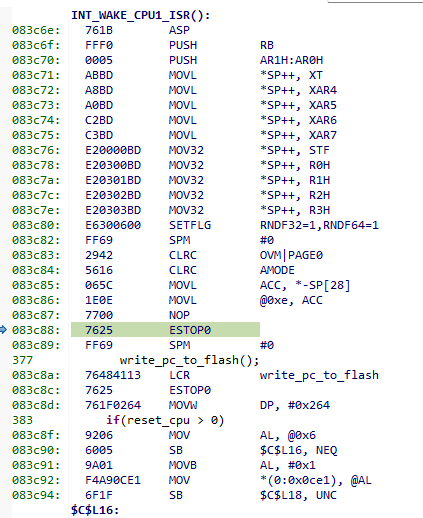

The next is the same ISR, but now it is writing out values to flash (a complex operation on the C28x). The disassembly leading up to the first coded ISR instructions (MOVL ACC, *-SP[28]) is significantly different and changes the stack quite a bit.

The issue I am trying to solve is referencing a value on the stack from the automatic context save, but depending on the contents of the ISR the stack position seems to be changing. I have a few questions:

1) What triggers the more in-depth context save that seems to be happening in the second ISR?

2) Is there a way to detect what kind of context save was done? My thought was by looking at the program counter value immediately upon entering the ISR- is there a way to tell the offset of the program counter from the address of the interrupt?

3) Is the best way to control this to declare the interrupt in assembly?

Open to other suggestions and thoughts as well.

Thanks!

Kris