Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Tool/software:

Hi Champs,

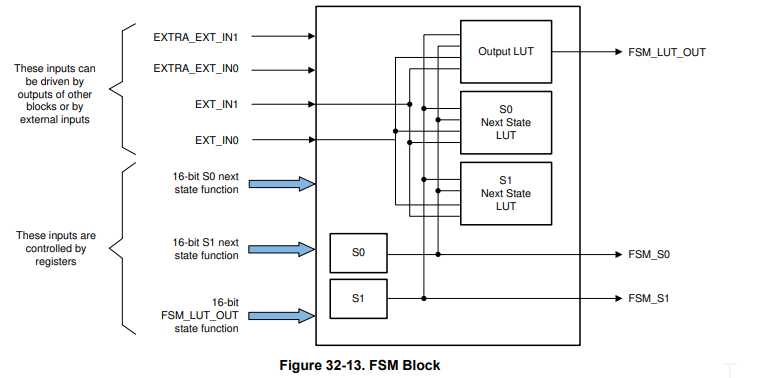

I ask this for customer. Now customer tried to use CLB FSM to implement functions such as clock synchronization and latching. However, from the TRM, it can only be seen that the FSM module is timing-dependent state control, and the specific internal RTL level is not explained in detail.

Now customer wants to know, can the following clock sync latch function be implemented? Do we have a configuration example and suggestion?

Thanks!

Best Regards,

Julia

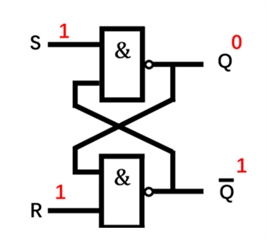

(without clock)

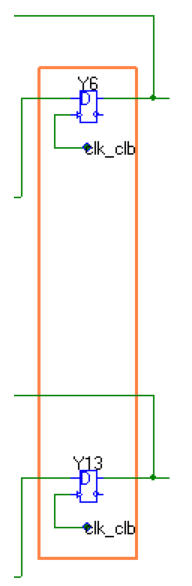

(without clock) (with clock)

(with clock)