Tool/software:

After halting the ECU using a TRACE32 debugger ('break" command) followed by triggering an external XRSn reset the following was observed:

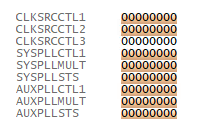

- System clock configurations are reset to default values

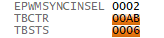

- PWM module is still enabled. PWM signal can be detected on output pins with a changed frequency corresponding to the reset clock configurations

- CPU appears to be still halted.

Is there an explanation why the PWM registers do not reset to their default values after an XRSn reset while the CPU is halted? Also is it possible for the CPU to remain halted by the debugger after an XRSn reset?