Tool/software:

Hi,

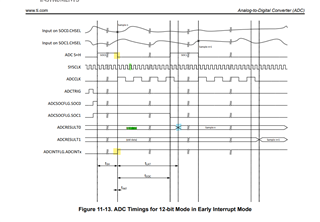

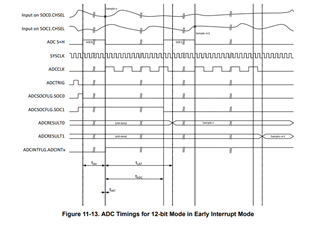

I've recently taken into account the Silicon errata sprz412n, and I'm having some difficulty understanding the point "ADC: DMA read of stale result", especially in terms of visualizing the scheduling.

From what I understand in the details section, the ADCINT is triggered before the end of the acquisition, which could result in stale data from the previous cycle. Am I correct in saying that this only affects the data of the SOC that generates the ADCINT (and the subsequent SOCs—but that wouldn't be considered abnormal behavior)?

What’s confusing for me is the Workarounds section. Using a "dummy DMA" to introduce a delay seems a bit extreme, which makes me think I may not fully understand the advisory.

Since we’re already using all DMA channels but not all ADC SOCs, we’re considering using a "dummy SOC" to trigger the ADCINT signal that, in turn, triggers the DMA. Can you please confirm that this is a correct workaround ?

Best regards , BR