Tool/software:

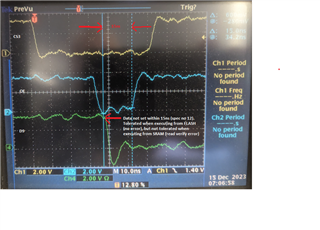

During write/read memory testing, we discovered that we were having read failures from external asynch memory on CS3. Our timing for Tsu (timing param 12) was violating the spec of 15 ns (ref 1). Our timing was varying and at times marginal and intermittently we would detect a failure. See attached screen shot. The device we were reading from was not driving the data lines soon enough. We fixed the device, and the read failure stopped happening. We were also able to avoid the problem by increasing R_SETUP (the read setup time).

This was discovered when we were executing our code from external SRAM.

However, when executing the same code from internal FLASH (without the correction mentioned above of course) , the failures were not occurring. The timing was identical in both cases. Screen shot attached. We are violating No 12 in both cases.

Is there an explanation for the failure not occurring when executing code from internal FLASH?

Thanks in advance,

Paul

Reference(s)

1. TMS320F2837xS 7.9.9.3.1.1 EMIF Asynchronous Memory Timing Requirements