Other Parts Discussed in Thread: F28385D

Tool/software:

Hi Experts,

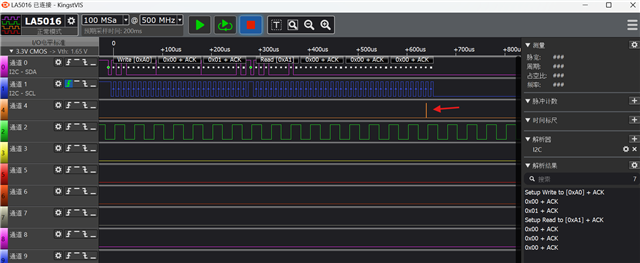

My customer is using F28385D. They found when they try to read 2 words from EEPROM, there would be three read words on the bus unexpectedly.

As the following picture (TOP) shows, they write 2 words to EEPROM and read 2 words back to verify

.

.

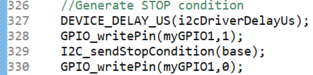

However, there would be 3 read words. This behaviour would sometimes cause the bus locked by EEPROM, as the lower half of the picture shows. F28388 is not able to generate stop condition even we try to manually pull the SDA line with GPIO function.

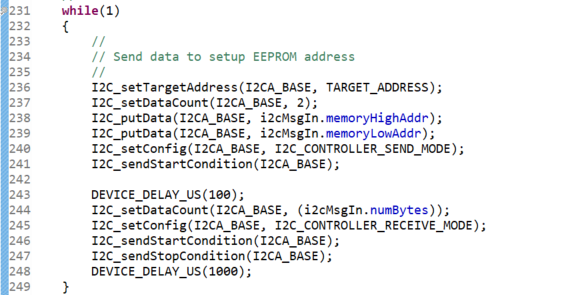

Their EEPROM read function is copied from the ex4 i2c example. As shown below the read size is configured as 2.

They want to reproduce the issue on control card but there is only on EEPROM for EtherCAT on the board. They are not sure if they should use it.

Is there any idea how to solve it?

Regards,

Hang