Part Number: TMS320F280025

Tool/software:

customer set PWM logical as below:

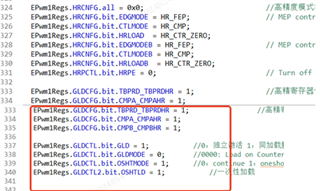

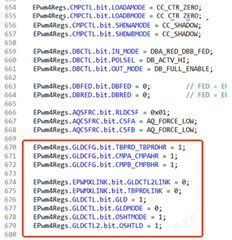

1, PWM1 general sync signal by counter zero event to PWM4, both PWM1 and PWM4 clear count and update register by sync event

2, PWM1 and PWM4 both set to Global one-shot load with counter zone event, and PWM4 link to PWM1

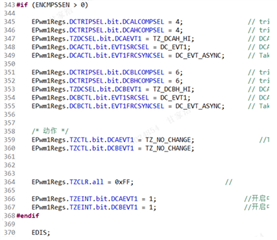

3, Timer0 general 40Khz interrupt to update PWM frequency and duty for PWM1 and PWM4 then trigger global one shot load

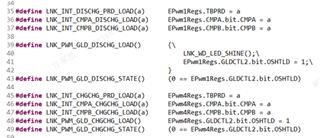

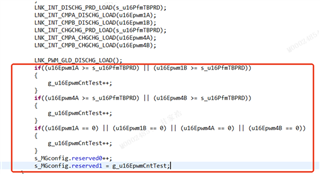

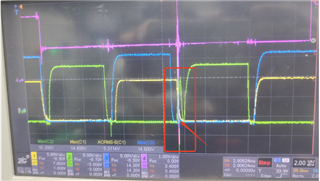

If step 3 code execute as below will general abnormal waveform

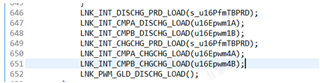

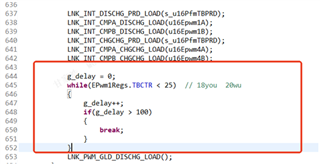

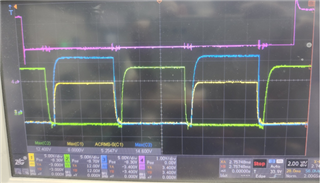

if step 3 code modify as below to avoid update close with counter zero, then pwm waveform always run well

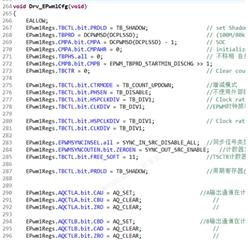

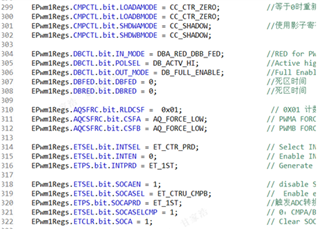

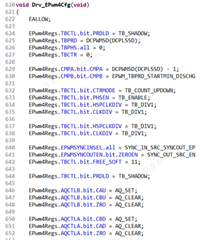

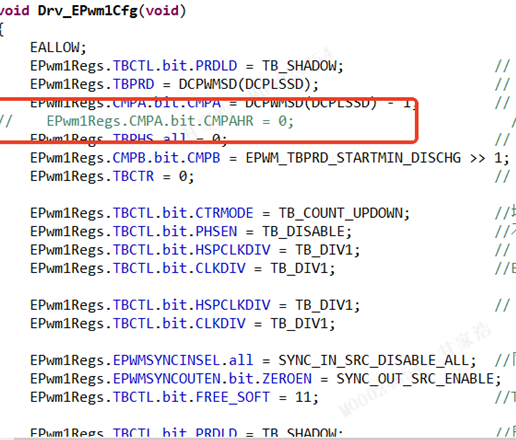

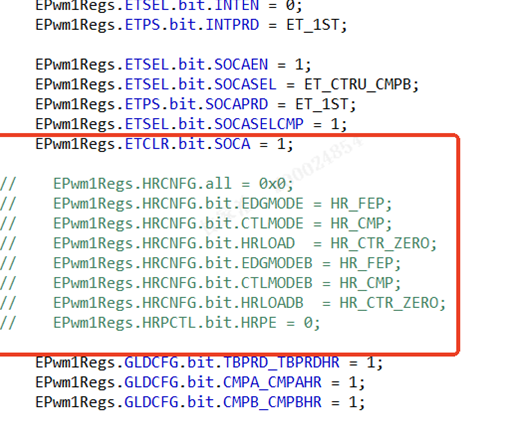

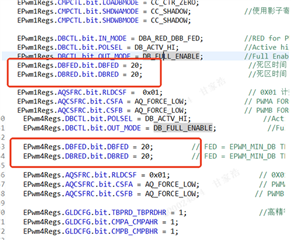

Below is the PWM1 and PWM4 setting code, could you please help review if anything setting missing to cause the issue?