Part Number: TMS320F28P650DK

Tool/software:

Dear TI support team,

I’m working with M-Can peripheral belonging to TMS320F28P650DK9, and I have a question related to the memory allocation of Standard Message ID Filter and Extended Message ID Filter.

Document SPRUIZ1B states RAM memory allocation is 32-bit word addresses and according to figures

Figure 35-23, Standard Message ID Filter Element Structure is 32 bits wide

Figure 35-24, Extended Message ID Filter Element Structure is 64 bits wide.

Now I'm going to describe my example.

For the standard filter, my setting is

st_stdFiltElem_0.sfid2 = 0x3FF;

st_stdFiltElem_0.sfid1 = 0x000;

st_stdFiltElem_0.sfec = 0x5;

st_stdFiltElem_0.sft = 0x0;

and for the extended filter, the setting is

st_extFiltElem_0.efid2 = 0x11223344;

st_extFiltElem_0.efid1 = 0x55667788;

st_extFiltElem_0.efec = 0x1;

st_extFiltElem_0.eft = 0x1;

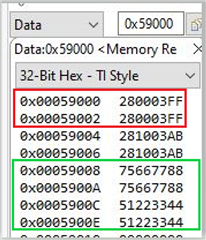

If I look the RAM memory from 0x5 9000 address, I see that

- Two 32 bit words are allocated for the standard filter: refer to the red square

- Four 32bit-words are allocated for the extended filter: refer to the green square

The following drivelib functions fill the RAM memory area

MCAN_addStdMsgIDFilter(MCANA_DRIVER_BASE, 0U, &st_stdFiltElem_0);

MCAN_addExtMsgIDFilter(MCANA_DRIVER_BASE, 0U, &st_extFiltElem_0);

So, my question is: according to the RAM memory view, it looks that there is memory consumption, or too much memory usage.

Is it correct?

If yes, why?

Best regards,

Ettore