Tool/software:

Hi expert,

I’ve been preparing a BL about the 280039 recently, and want to discuss two items with you:

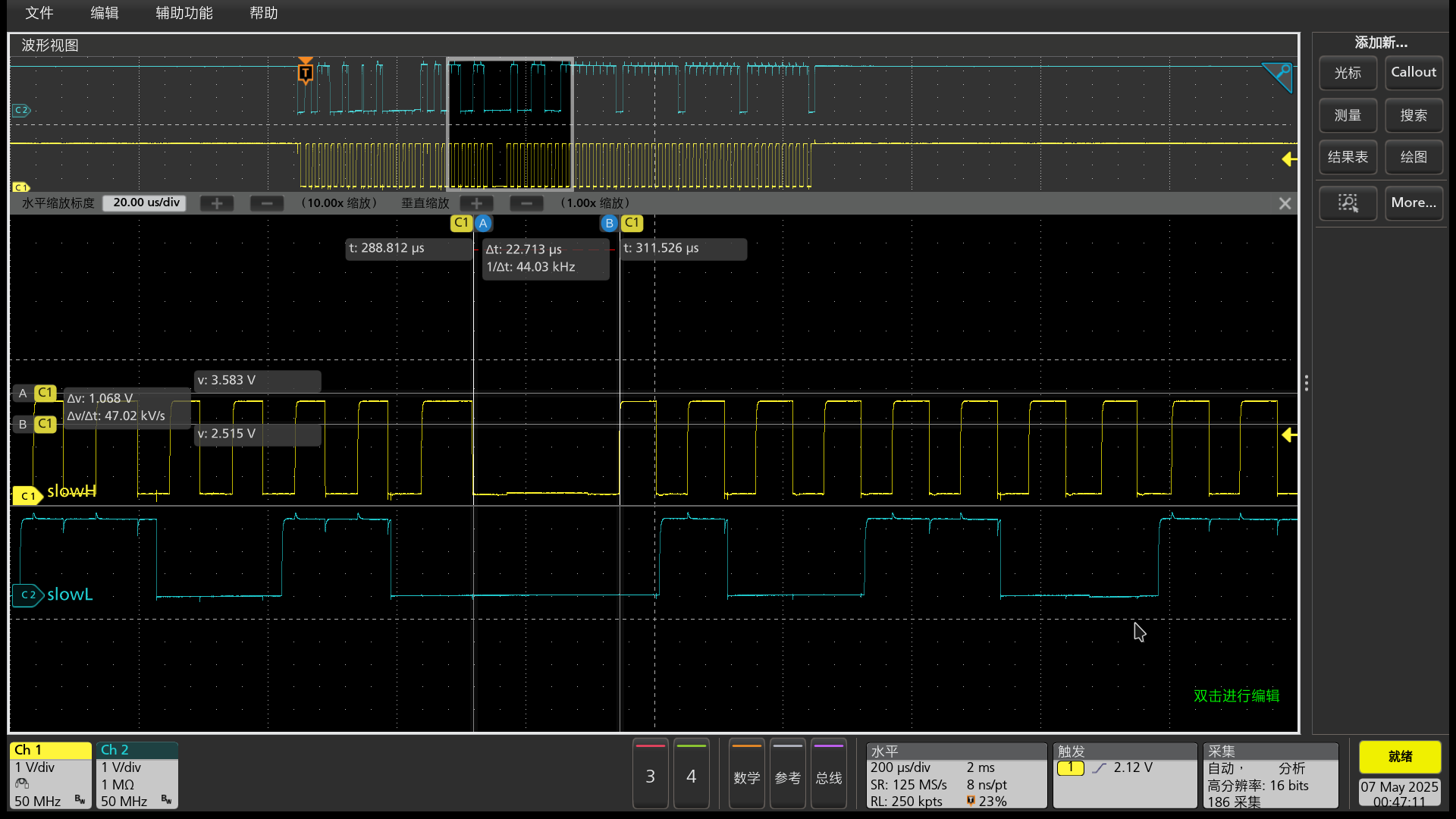

Q1: when I read data via I2C bus, the target will hold the SCL as low and the GUI readback the wrong data(picture1), So how long will the target will hold the SCL while in the salve-transmitter mode?

Q2: when I modify the CMD file just take the .text section from the Bank0 to Bank1, but these don’t seem to work(picture2)