Tool/software:

Hi experts,

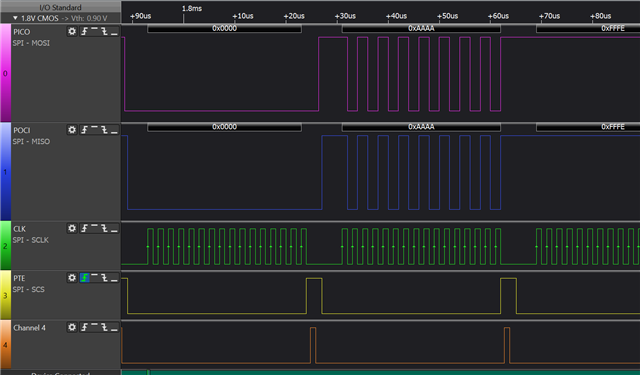

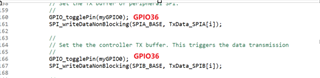

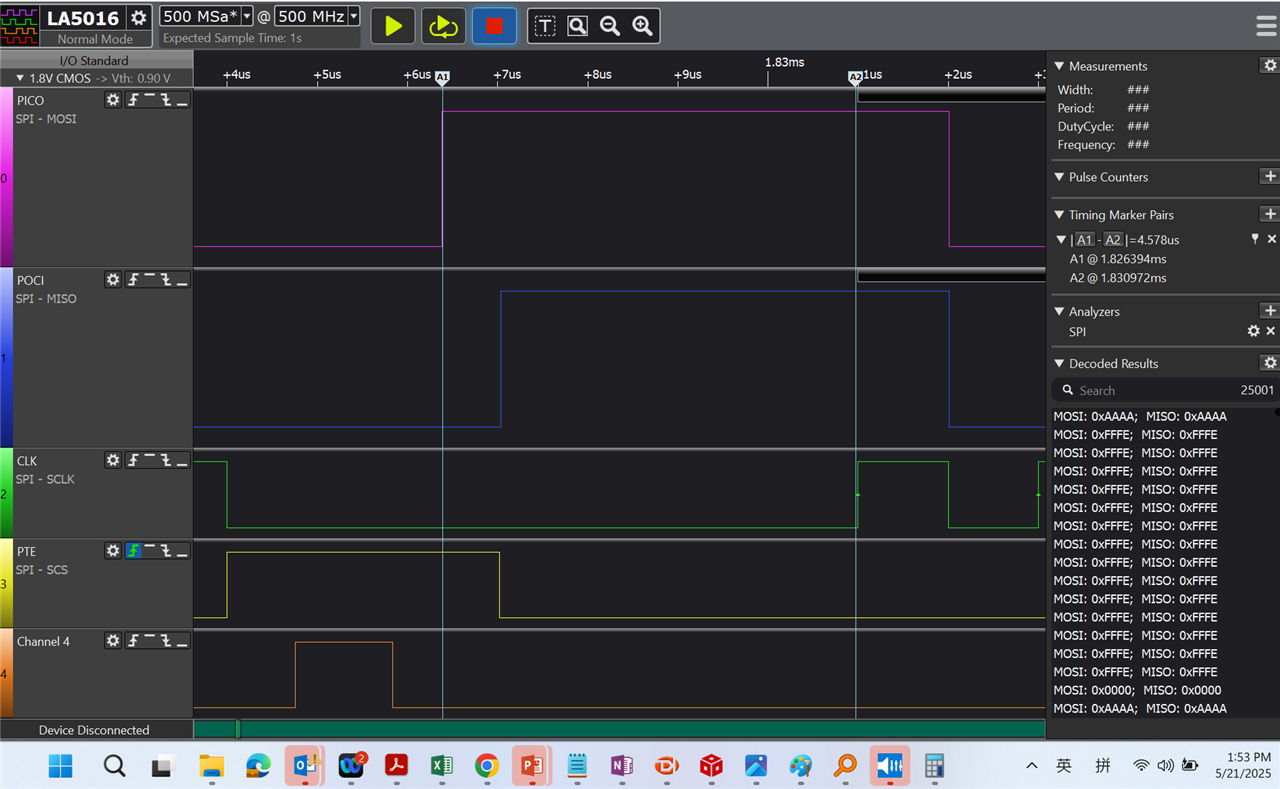

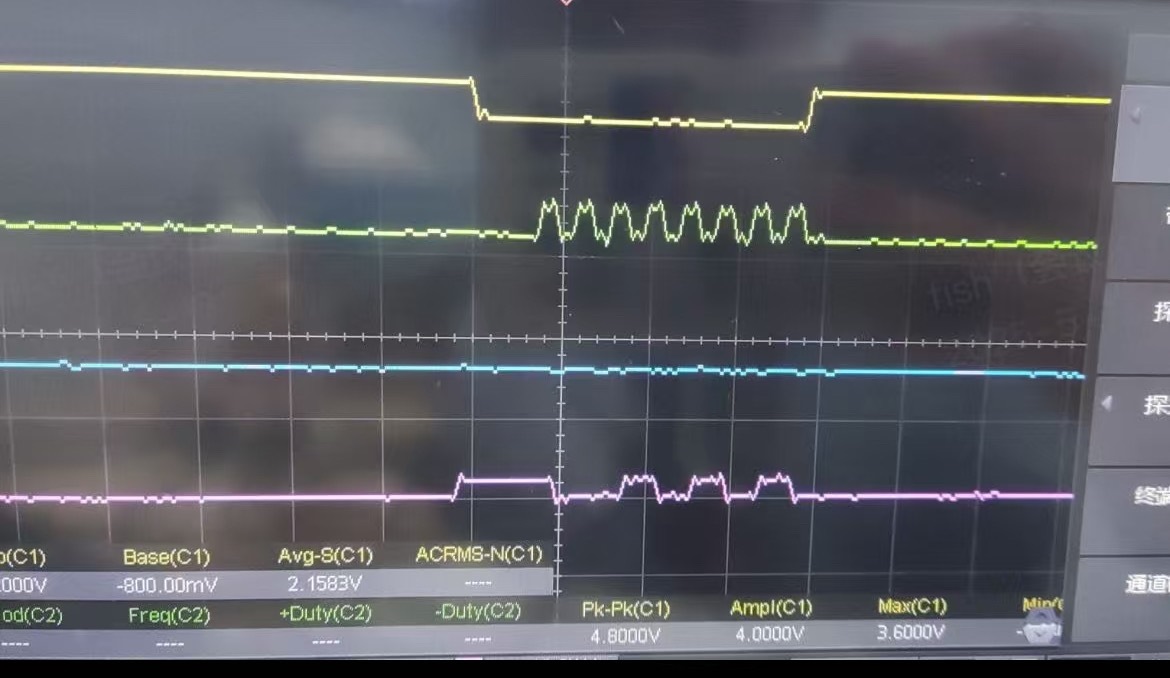

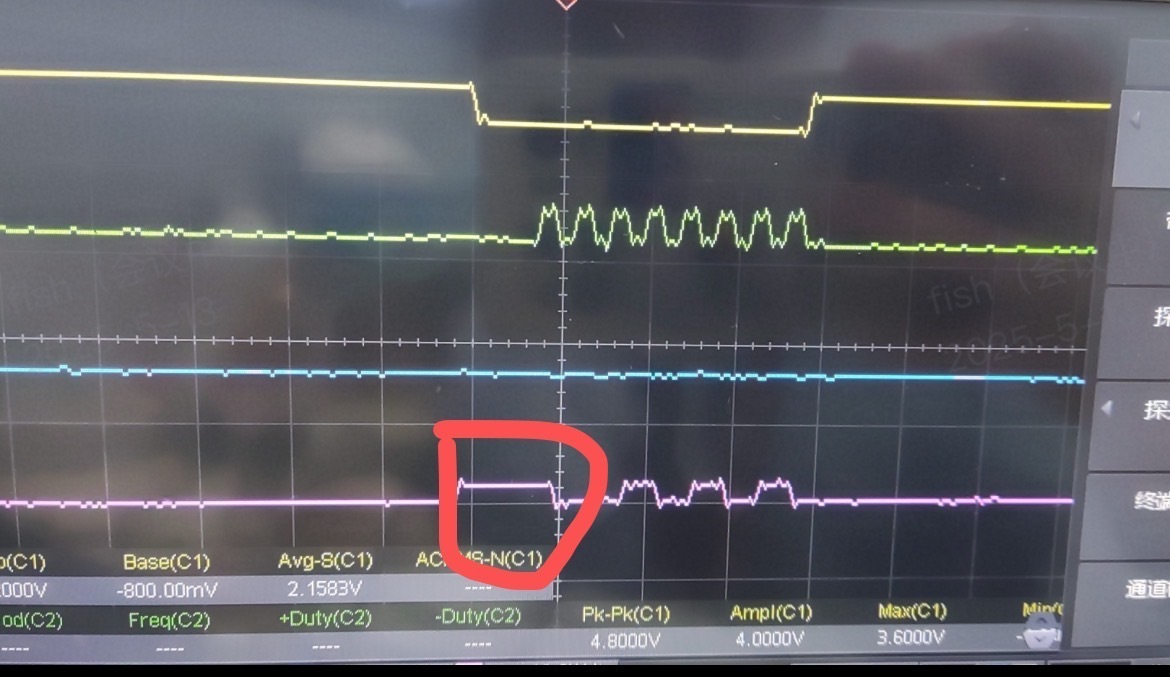

Good day! I am asking for customer. 28P65 is used as SPI master. My customer found that in her SPI scope, when PTE is low and CLK doesn't start, the SIMO will be driven high immediately. I mark the strange part with red circle. The waveforms are PTE, clk, somi, Simo from top to bottom .

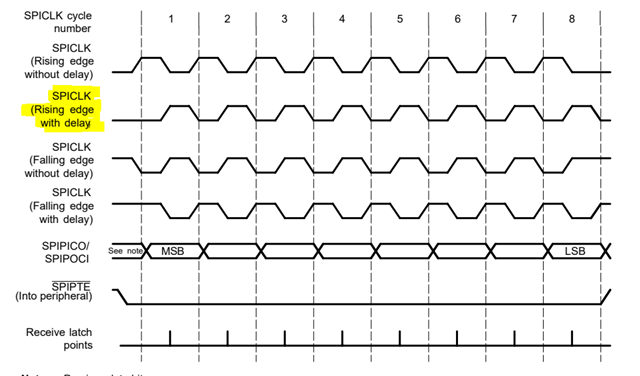

I have checked the standard SPI scope, when PTE is driven low, the SIMO should not follow up the change with PTE immediately, it should follow up CLK.

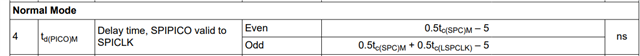

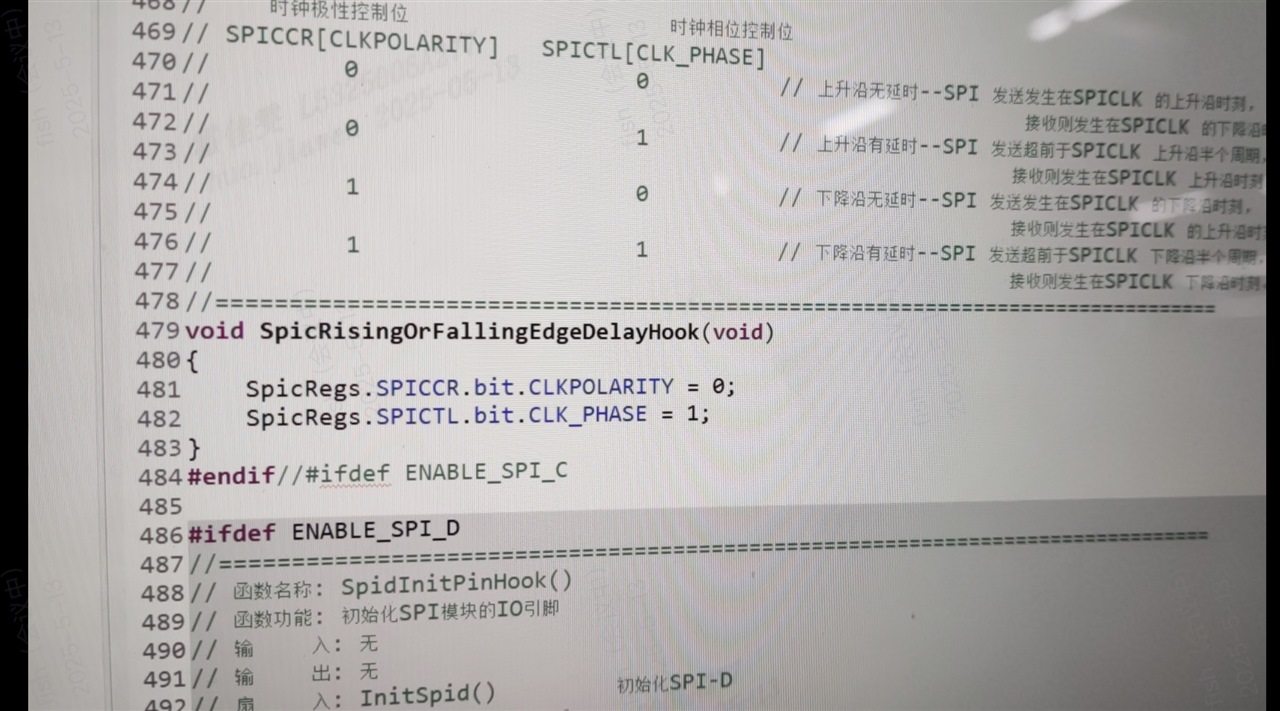

Here is phase and polarity configuration.

Could you help to explain this phenomenon ?

This is an urgent case, could you help to check ASAP?

Thanks!

Best Regards

Kita