Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Tool/software:

I am using the TMS320F28P650DK device as an SPI peripheral (slave) to send and receive data to/from another (controller) micro in my system. The other micro generates clock and chip select signals.

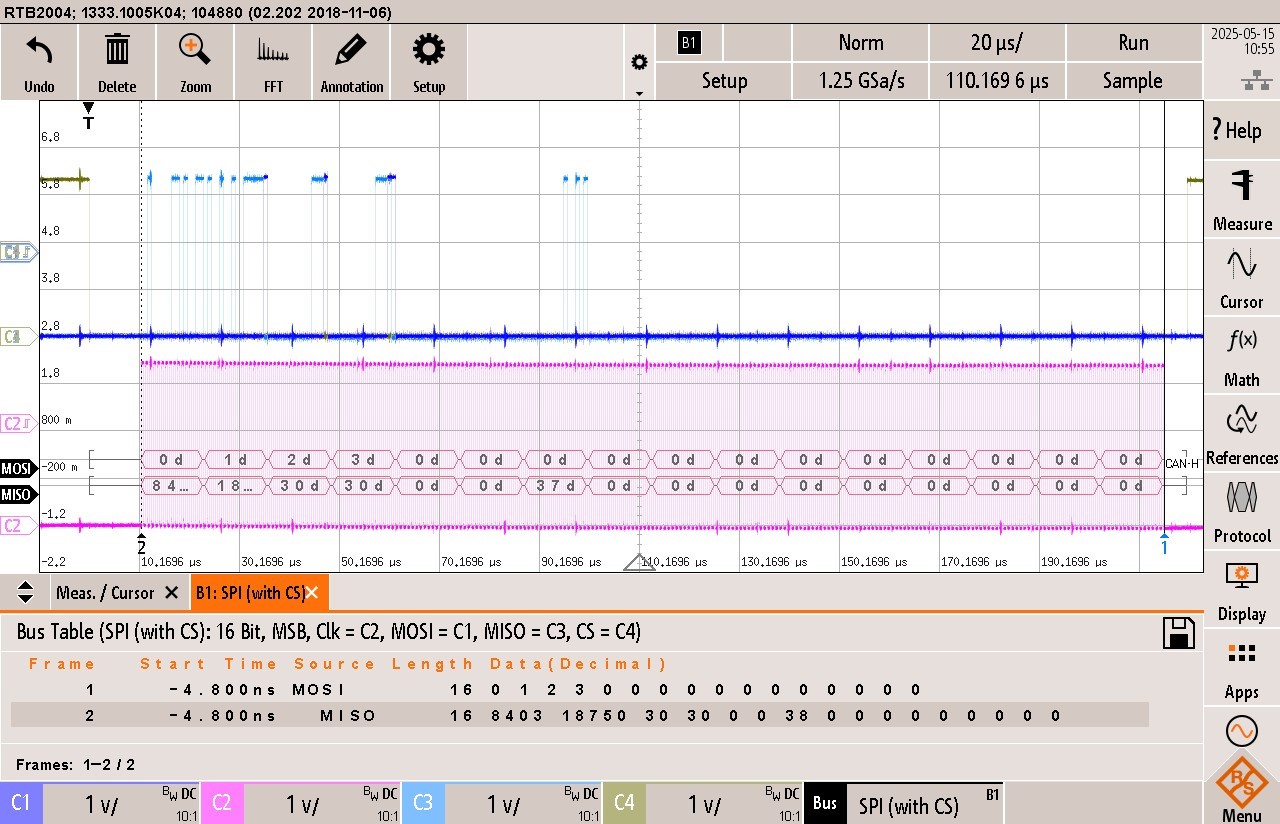

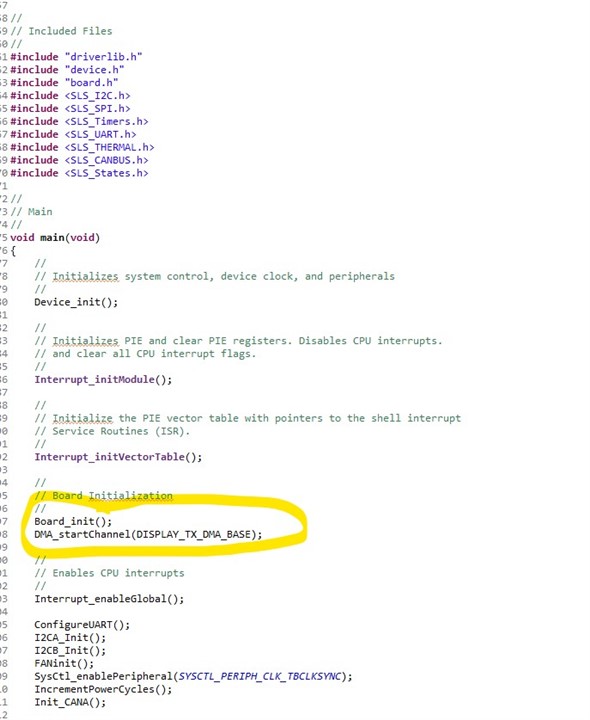

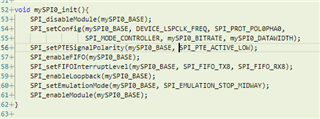

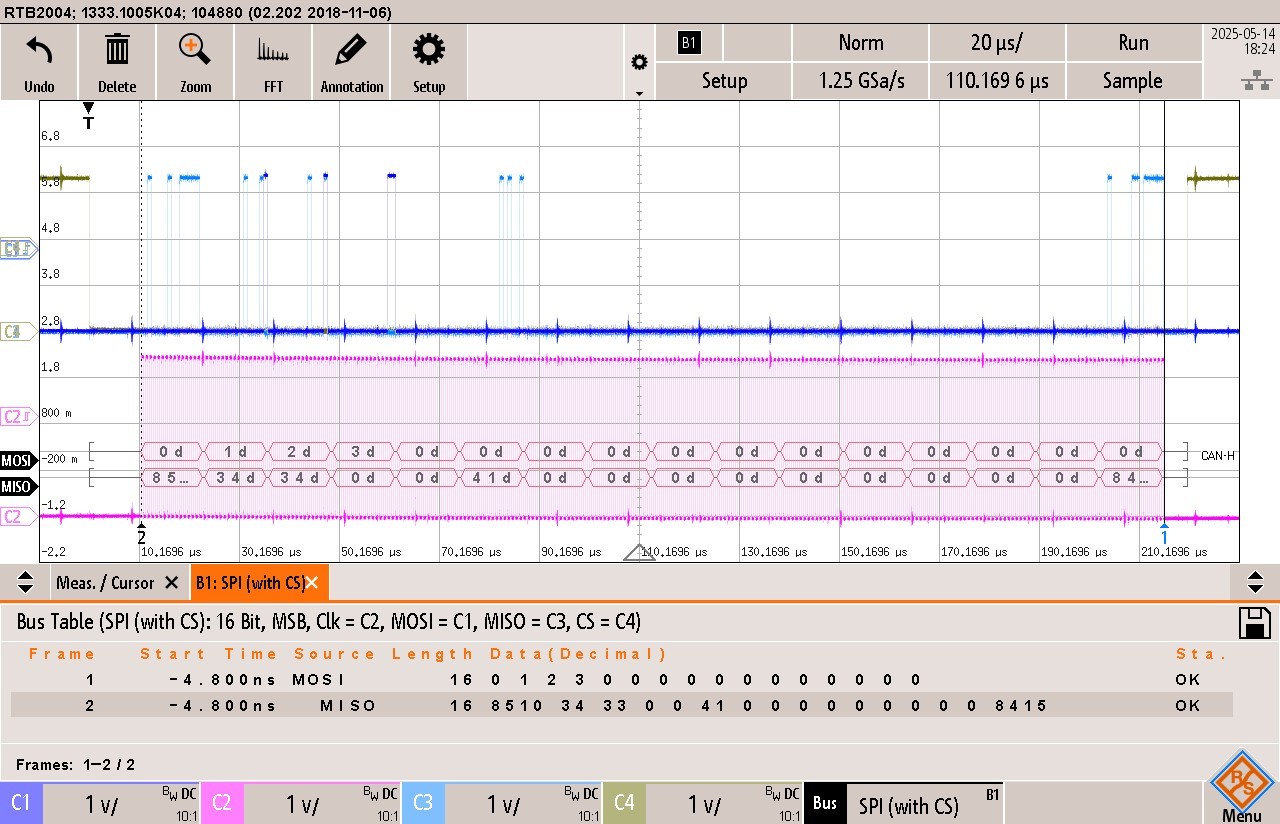

I am trying to send quite a bit of data so am setting things up so we have DMA manage data flow into and out of the SPI peripherals. As a starting point I want to send/receive 16x 16 bit words so set the C2000 slave to use data in 16 bit words with DMA. The other micro generates the correct chip select and clock lines to support this. The figure below shows an example transmission with the clock (C2, purple) cycling 256 times for the 16x 16 bit words.

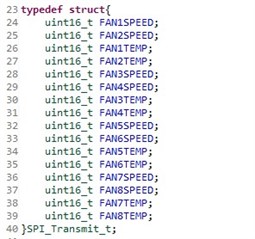

The data transmission works but the position of the data in the DMA transfer from the C2000 (MISO) looks like it has wrapped around by one word. The struct I setup for the data transmission from the C2000 part is:-

The first 16 bit word word on the MISO transmission is the FAN2SPEED data (I checked this in practice by changing that data and seeing just the first word bits change). The second word is FAN1TEMP and the third word is FAN2TEMP. The FAN1SPEED which should have been the first word of the transmission is the 16th word, right at the end of the transmission. It looks like it has wrapped around.

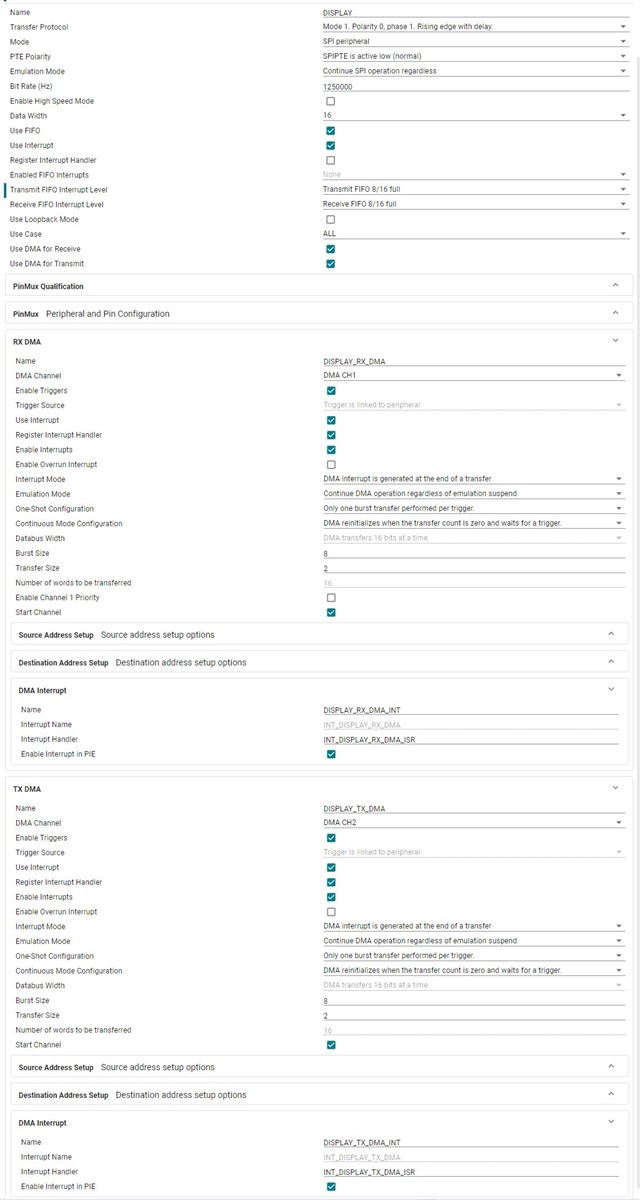

My question is what would cause this behaviour? I get a feeling it might be how the FIFO is set up or maybe the FIFO isn't empty before the transmission starts. Both DMA channels are running continuously, enabled in sysconfig. Maybe I should be starting them and stopping them based on activity on the incoming nCS or clock lines from the SPI controller?

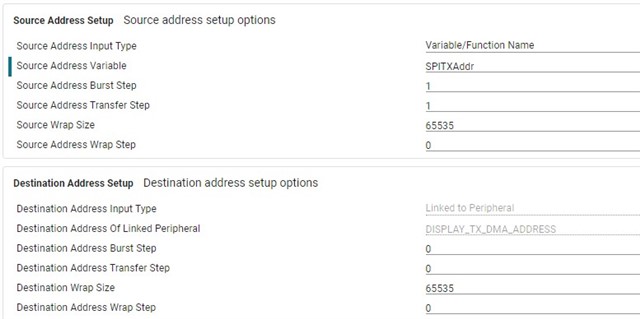

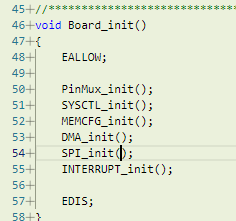

Here is the SPIC peripheral setup in sysconfig:-

Any ideas are most welcome.

Thanks, Iain