Tool/software:

Hello,

While analyzing the TMS320F28386D design, I found multiple inconsistencies in the TRM about interrupts. Could you clarify the following information?

What are the CM_RAM_TESTERROR_LOG, CIPC, MPOST and SDFM interrupts?

The TRM states in the SDFM section (28.1) that only SDy_ERR and SDyFTLx_DRINT are present but the interrupt list for CLA / CPUs do not show the same.

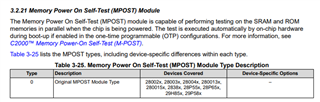

It seems that only CPU1 is connected to MPOST features. What is it exactly?

I2CA seems to have two interrupts lines INT1.9 and INT8.1. Should it be I2CA and I2CB?

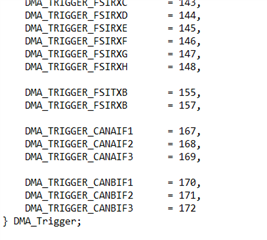

CANA_IFx are repeated in Table 11-1. Should it read CANB?

Thanks,

Alexy