Other Parts Discussed in Thread: C2000WARE,

Tool/software:

Good day,

I am reaching out to see if someone can help me figure out why my firmware update is not working.

1 - In the C:\ti\C2000Ware_5_04_00_00\driverlib\f28003x\examples\flash folder I built the flash_kernel_ex3_sci_flash_kernel and flashed it to both BANK0_LDFU and BANK1_LDFU build configurations.

2 - I modified the flashapi_ex5_lfu_no_reset project found in the C:\ti\C2000Ware_5_04_00_00\driverlib\f28004x\examples\flash to work on a f28003x LAUNCHXL board. There are 2 builds, one for BANK0 and one for BANK1.

Modifications made are:

Changed name of project to "flashapi_ex5_lfu_no_reset_F200839C".

Under project properties, I made all properties for the f28003x board the same as the f28004x except I changed the paths for the variables:

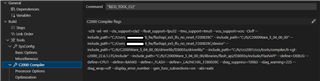

The C2000 Complier:

The C2000 Linker:

Under C2000 Complier, Pre defined symbols I added _LAUNCXL_F280039C so I could use the correct pins for LEDs and SCI TX and RX (LEDs are 20 22, SCI are 28 and 29).

I then flashed both projects to board. All flashes were set to erase necessary settings only:

The cmd files for Bank0 build and Bank1 build had to be modified so it would work with the F280039C, but the addresses are similar.

I then built the both configurations and flashed to board.

3 - I then used the flash_kernel_ex3_sci_flash_kernel to create a text output file. I build that in the CPU1_RAM configuration. I placed that file in the same folder as the serial programmer at C:\ti\C2000Ware_5_04_00_00\utilities\flash_programmers\serial_flash_programmer

4 - I then copied the text file from one of the modified flashapi_ex5_lfu_no_reset builds and pasted it in the same folder as the serial programmer.

5 - I opened a command prompt and directed it to the serial programmer directory at C:\ti\C2000Ware_5_04_00_00\utilities\flash_programmers\serial_flash_programmer.

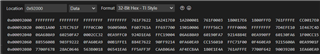

6 - then entered serial_flash_programmer.exe -d f28003x -k flash_kernel_ex3_sci_flash_kernel.txt -a flashapi_ex5_lfu_no_reset_F200839C.txt -b 9600 -p COM8 -v and pressed enter.

I got this output:

Can someone help me with what may be going wrong? Or any tips to try to get this to work?

Cheers,

Scott