Part Number: TMS320F28379D

Tool/software:

Hello E2E Experts,

Good day.

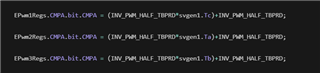

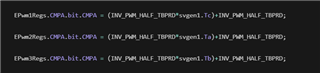

EPwm1Regs theoretically corresponds to phase A, why does it correspond to svgen1.Tc in the code?

Regards,

TICSC

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320F28379D

Tool/software:

Hello E2E Experts,

Good day.

EPwm1Regs theoretically corresponds to phase A, why does it correspond to svgen1.Tc in the code?

Regards,

TICSC

Hi,

You are right, traditionally and theoretically in the 3/2 transformation, phase A is aligned with the alpha axis, and resultant EPwm1Regs corresponds to phase A. However, this code base uses different axis for dq transformation, thus cause this difference on the pulse width mapping.

Thanks,

Jiaxin

Hello Jiaxin,

Good day.

Hi,

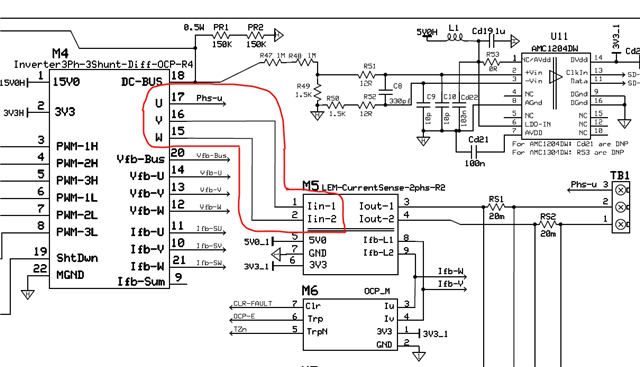

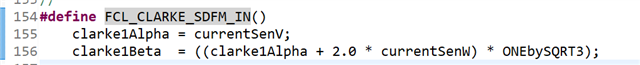

If you are using the exact same hardware, you may find the the current sensing only sample the V and W phase and also takes phase V (not phase U) align with alpha axis no matter if it is SDFM sensing or LEM sensing.

This is different with the FOC implementation in the universal motor lab solution, where the phase A/U is set to align with the alpha axis.

Schematic of IDDK hardware

3/2 transform with SDFM sensing

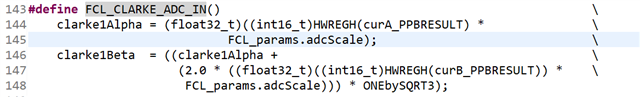

3/2 transform with LEM sensing, "curA_PPBRESULT" is the ADC result of phase V, which can be found in FCL_initADC() and configureADC().

Thanks,

Jiaxin