Tool/software:

Dear TI Support Team,

I am currently developing a project using the TMS320F28035 and have encountered a memory-related issue that I hope to get your insight on.

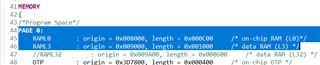

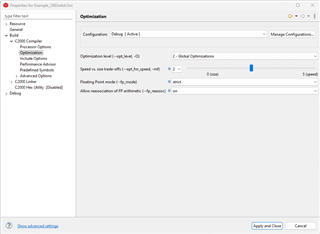

I have written a program that utilizes the memory of the TMS320F28035. I’m currently facing a memory overflow issue in the RAML0 section of the code. Although I have optimized the program as much as possible, the problem still persists.

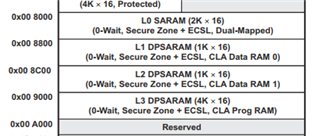

After reading the C2000-2803x technical documentation, I found that it’s possible to combine RAML0 and RAML1 to increase the available memory space for the program. RAML1 is currently unused. However, I also noticed that RAML0 is dual-mapped, and it seems to provide faster execution speed compared to other memory blocks, which is critical because my application requires high execution speed.

Therefore, I have a few questions that I’d like clarified:

-

If I combine RAML0 and RAML1, will my program actually run slower compared to executing solely in RAML0 SARAM, due to the loss of dual-mapped characteristics?

-

Are there any alternative solutions to deal with the memory overflow problem?

I would greatly appreciate your advice or any possible solutions regarding this issue.

Thank you very much for your support.