Other Parts Discussed in Thread: TDC7200,

Tool/software:

Dear Community

Current Situation:

We are using the TMS320F28376S microcontroller and a TDC7200 Time-to-Digital-Converter. our application uses SYS/BIOS (6.83.0.18) as RTOS.

We have configured a Timer as a Hwi which posts a SWI to start a measurement by sending the cmd to the TDC7200. The Hwi only posts the SWI. Within the SWI we handle the logic, cleaning up, reading TOF values form previous measurement and start a new measurement. We start every 1.6ms a measurement. We set up a Timer which is called every 200us, but at every 8th slice we send the measurement cmd.

void TIMER1_SWI() { // Timer Swi Controller::handleTimerIsr(); }

void TIMER1INT_ISR(UArg) { // Timer Hwi Swi_post(TIMER1_swi); }

Surely, we set up an external Interrupt which posts a SWI, which handles the logic. This means, initiating a SPI transfer to to read the Values to calculate TOF1 and TOF2. The TDC7200 has an Interrupt line which pulls high, when the measurement is started and pulls low, when the measurement is finished.

extern const Swi_Handle XINT3_swi;void XINT3_ISR(void) // 0x000DF0 XINT3{ Swi_post(XINT3_swi); // post a SWI}

void XINT3_SWI() { // TDC Swi Controller::handleXintIsr(); }

Here is the SYS/BIOS configuration which we set up the ISR's which come from the TDC7200. The XINT3_ISR is the only one which is called in the Interrupt Group 12.// XINT Configuration which is triggered too often

var hwi11Params = new Hwi.Params();hwi11Params.enableAck = true;hwi11Params.instance.name = "XINT3_HWI";Program.global.XINT3_HWI = Hwi.create(120, "&XINT3_ISR", hwi11Params);

// The corresponding SWI which is posted in XINT3_ISR

var swi10Params = new Swi.Params();swi10Params.instance.name = "XINT3_swi";swi10Params.priority = 10;Program.global.XINT3_swi = Swi.create("&XINT3_SWI", swi10Params);

The Problem:

We observate that the ISR is started, even the TDC7200 does not have a falling edge on the Interrupt line. This can be seen at the picture below. We setup the TDC7200 using a 64 averaging.

In the first picture, one can see an expected measurement where the TDC7200 Interrupt has a short pulse. Within these pulse, there are 64 cycles done and we receive valid data from the TDC7200. This works charming. However, at the "bad" measurement after four cycles our SWI gets called, even the HWI should not be triggered due to a missing falling edge on the TDC7200 interrupt line.

The picture below is zoomed from the previous one. It is visible, that after 4 cycles we get called into the SWI, even the TDC7200 Interrupt does not get to 0. We know, that we are in the SWI since the SPI transfer from the TOF values are only implemented within this SWI. The values are of course wrong (we calculated negative TOF values). Interestingly, we get this bad measurement after 4 cycles. it is not quite regulary, but 1 to 2% of the measurements are like this.

Call stack and register values:

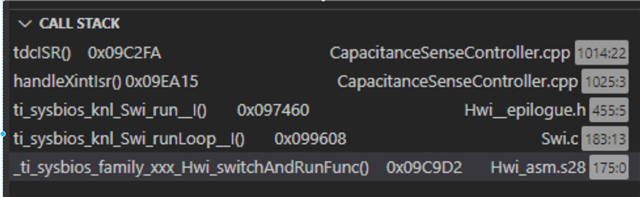

This is the callstack, when the measurement fails.

The register values when SWI started are like following at a bad measurement:

PieCtrlRegs->PIEACK.ACK12 = 1

IFR->INT12 = 1

PIEIFR12->INTx1 = 1

Actions done:

As far as we know, SYS/BIOS should take care of the resetting the PIEIFR flag for the ISR as well as the acknowledge bit of the Interrupt group. I am not aware, what exactly the functions of SYS/BIOS do, but I have the feeling, that SYS/BIOS is not aware of this function call. This also explains the PIE registers which are not reset. However, most of the time, the measurement does work properly and the ISR's are called only when a falling edge is detected.

Also, the call stack is different to a good measurement. At a good measurement switchAndDispatch is called, which is more what I expected. As well, there is restoreHwi called, which I guess takes care of cleaning up the register values. It is not easy to understand SYS/BIOS because the available documentation is quite poor.

Have we missed configuring the SYS/BIOS properly? How can we be sure, that the Hwi is called, which posts the SWI?

How does the scheduler work, when we post a SWI in a HWI?

I really appreciate any hints for this problem.

Best regards, Robert