Other Parts Discussed in Thread: TIDA-00179

Tool/software:

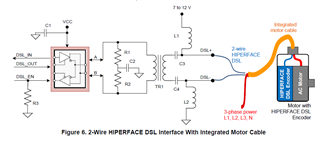

My current project need to use F28388D to support Endat2.2, Hiperface DSL and quadrature encoders. Right now I'm using FPGA and SDRAM for HDSL and EnDat IP core but I would like to get rid of the FPGA. I found some documents shows how to implement EnDat2.2 with CLB and SPI on Delfino processors. I'm thinking if it support Hiperface DSL as well? Or the FPGA is necessary just for applying HDSL with F28388D?

Thanks,

Jing